# Interscience Research Network

**Conference Proceedings - Full Volumes**

**IRNet Conference Proceedings**

Fall 10-7-2012

## Proceeding of International Conference On Eletrical,Electronics,Computational Vision and Robotics ICEECVR-2012

Prof. (Dr.) Srikanta Patnaik

Follow this and additional works at: https://www.interscience.in/conf\_proc\_volumes

Part of the Computer Engineering Commons, and the Electrical and Computer Engineering Commons

## **Editorial**

Inventions and discoveries have emanated from creative minds that have been constantly working and imaging the outcome in the mind. With imaging and constant effort, all the forces of the Universe work for that inspired mind, thereby leading to inventions or discoveries. Higher the number of creative minds in an organization, the best results of invention and discoveries will emerge. Unique academic environment results into great thinking that leads to creativity.

Mobile Operators around the world are enjoying the fruits of the rapid growth in mobile broadband, which was a challenge before the Engineers. Before talking about challenges, one should first recognize that the data boom is a huge opportunity for the entire mobile industry. Customers are still willing to pay a reasonable amount for access to the services, products and content carried by mobile networks. However, it is true that the growth has been so fast and so big that it has created tension on infrastructure. The new devices and applications behave in a way that is often not optimized for mobile networks. Many applications on smartphones for instance are almost always alive and exchanging information with the network even when the customer is not actively using them. They create an ever present noise in the form of signaling that can stress the network. The researchers have to cope with this by Hybridizing several technologies, including HSPA, LTE and WLAN, to create the access capacity necessary to provide the best broadband coverage everywhere. HSPA should be pushed to ever higher bandwidths and introduce LTE to WLAN proposition to build coverage. It also needs to develop all the engineering behind that backhaul. Technicians has to work with vendors to collectively, invest in new and resilient architectures for developing the networks. It can be new systems and network architectures that will allow for separate dimensioning of traffic and signaling. But that's not the whole story. There is a need to work with the developer community to help them design their applications to work more intelligently with the networks. It is in their interest that their applications are more efficient and can deliver a better experience on smartphones and tablets for the customer's benefit.

Smart grids electricity transmission and distribution that uses two-way communications to optimize supply and demand which are vital in managing energy consumption, integrating renewable and micro power generation, and supporting the greater use of electric vehicles. The benefits of smart grids could be substantial. In the United States alone, successful deployment of smart grid technologies could yield savings to society of USD 130 billion annually,that claims a recent McKinsey magazine. The deployment of smart metering is already well advanced in Finland, Italy, Sweden and California. Smart meters provide information for utilities to measure energy consumption in real time and for customers to follow the amount and cost of their consumption. Trials have shown

that peak loads can be reduced by 20% simply by making consumption data available to consumers. Therefore it is rightly said:-

## "Discovery consists of seeing what everybody has seen and thinking what nobody has thought." Albert Von Szent-Gyorgy

So this conference has been designed to stimulate the young minds including Research Scholars, Academicians, and Practitioners to contribute their ideas, thoughts and nobility in these disciplines of engineering. It is a pleasure to welcome all the participants, delegates and organizer to this International Conference on behalf of IOAJ family members. This conference has received a great response from all parts of the country and abroad for the presentation and publication in the proceedings.

I sincerely thank all the authors for their valuable contribution to this conference. I am indebted towards the reviewers and Board of Editors for their generous gifts of time, energy and effort.

### **Editor-in-Chief**

### Prof. (Dr.) Srikanta Patnaik

Chairman, I.I.M.T., Bhubaneswar Intersceince Campus, At/Po.: Kantabada, Via-Janla, Dist-Khurda Bhubaneswar, Pin:752054. Orissa, INDIA.

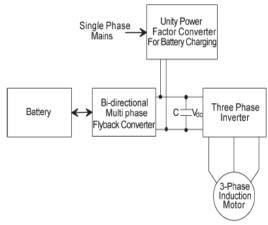

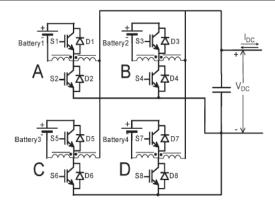

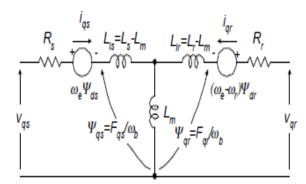

### ADVANCED DIRECT POWER CONTROL OF MATRIX CONVERTER BASED UNIFIED POWER-FLOW CONTROLLER

### K.MEENENDRANATH REDDY, O.HEMAKESAVULU & M. PADMA LALITHA

Department of Electrical Engg, P.G Student, AITS College, Rajampeta,

**Abstract**— An electrical power system is a large interconnected network that requires a careful design to maintain the system with continuous power flow operation without any limitations. Flexible Alternating Current Transmission System (FACTS) is an application of a power electronics device to control the power flow and to improve the system stability of a power system. This paper presents a direct power control (DPC) for three-phase matrix converters operating as unified power flow controllers (UPFCs). Matrix converters (MCs) allow the direct ac/ac power conversion without dc energy storage links; therefore, the MC-based UPFC (MC-UPFC) has reduced volume and cost, reduced capacitor power losses, together with higher reliability. Theoretical principles of direct power control (DPC) based on sliding mode control techniques are established for an MC-UPFC dynamic model including the input filter. As a result, line active and reactive power, together with ac supply reactive power, can be directly controlled by selecting an appropriate matrix converter switching state guaranteeing good steady-state and dynamic responses. Experimental results of DPC controllers for MC-UPFC show decoupled active and reactive power linear controllers based on a modified Venturini high-frequency PWM modulator, the experimental results of the advanced DPC-MC guarantee faster responses without overshoot and no steady-state error, presenting no cross-coupling in dynamic and steady-state responses. *Index Terms*— *Direct power control (DPC), matrix converter (MC), unified power-flow controller (UPFC).*

### I. INTRODUCTION

The technology of power system utilities around the world has rapidly evolved with considerable changes in the technology along with improvements in power system structures and operation. The ongoing expansions and growth in the technology, demand a more optimal and profitable operation of a power system with respect to generation, transmission and distribution systems. In the present scenario, most of the power systems in the developing countries with large interconnected networks share the generation reserves to increase the reliability of the power system. However, the increasing complexities of large interconnected networks had fluctuations in reliability of power supply, which resulted in system instability, difficult to control the power flow and security problems that resulted large number blackouts in different parts of the world. The reasons behind the above fault sequences may be due to the systematical errors in planning and operation, weak interconnection of the power system, lack of maintenance or due to overload of the network.

In order to overcome these consequences and to provide the desired power flow along with system stability and reliability, installations of new transmission lines are required. However, installation of new transmission lines with the large interconnected power system are limited to some of the factors like economic cost, environment related issues. These complexities in installing new transmission lines in a power system challenges the power engineers to research on the ways to increase the power flow with the existing transmission line without reduction in system stability and security. In this research process, in the late 1980's the Electric Power Research Institute (EPRI) introduced a concept of technology to improve the power flow, improve the system stability and reliability with the existing power systems. This technology of power electronic devices is termed as Flexible Alternating Current Transmission Systems (FACTS) technology. It provides the ability to increase the controllability and to improve the transmission system operation in terms of power flow, stability limits with advanced control technologies in the existing power systems.

In the last few decades, an increasing interest in new converter types, capable of performing the same functions but with reduced storage needs, has arisen. These converters are capable of performing the same ac/ac conversion, allowing bidirectional power flow, guaranteeing near sinusoidal input and output currents, voltages with variable amplitude, and adjustable power factor. These minimum energy storage ac/ac converters have the capability to allow independent reactive control on the UPFC shunt and series converter sides, while guaranteeing that the active power exchanged on the UPFC series connection is always supplied/absorbed by the shunt connection. Conventional UPFC controllers do not guarantee robustness.

In the dependence of the matrix converter output voltage on the modulation coefficient was investigated, concluding that MC-UPFC is able to control the full range of power flow. Recent nonlinear approaches enabled better tuning of PI controller parameters.

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

Still, there is room to further improve the dynamic response of UPFCs, using nonlinear robust controllers. In the last few years, direct power control techniques have been used in many power applications, due to their simplicity and good performance

In this paper, a matrix converter- based UPFC is proposed, using a direct power control approach (DPC-MC) based on an MC-UPFC dynamic model. In order to design UPFCs, presenting robust behavior to parameter variations and to disturbances, the proposed DPC-MC control method is based on sliding mode-control techniques, allowing the realtime selection of adequate matrix vectors to control input and output electrical power. Sliding modebased DPC-MC controllers can guarantee zero steady-state errors and no overshoots, good tracking performance, and fast dynamic responses, while being simpler to implement and requiring less processing power, when compared to proportionalintegral (PI) linear controllers obtained from linear active and reactive power models of UPFC using a modified Venturini high-frequency PWM modulator.

The dynamic and steady-state behavior of the proposed DPC-MC P, Q control method is evaluated and discussed using detailed simulations and experimental implementation. Simulation and experimental results obtained with the nonlinear DPC for matrix converter-based UPFC technology show decoupled series active and shunt/series reactive power control, zero steady-state error tracking, and fast response times, presenting faultless dynamic and steady-state responses.

### II. MODELING OF THE MATRIX CONVERTER UPFC POWER SYSTEM

### A. General Architecture

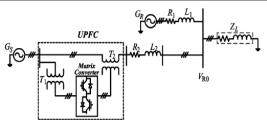

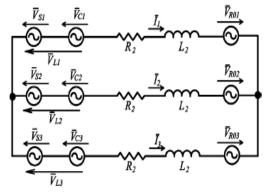

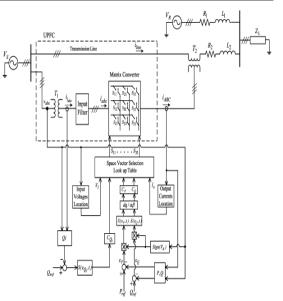

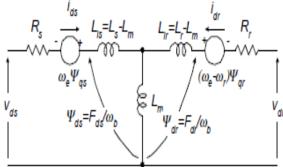

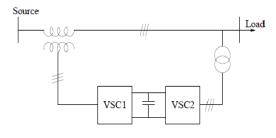

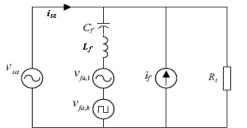

A simplified power transmission network using the proposed matrix converter UPFC is presented in Fig. 1, where  $V_{\mathcal{S}}$  and  $V_{\mathcal{R}}$  are, respectively, the sending-end and receiving-end sinusoidal voltages of the  $G_{\mathcal{S}}$  and  $G_{\mathcal{R}}$  generators feeding load  $Z_{\mathcal{L}}$ . The matrix converter is connected to transmission line 4, represented as a series inductance with series resistance ( $L_2$  and  $R_2$ ), through coupling transformers and  $T_1$  and  $T_2$ . Fig. 2 shows the simplified three-phase equivalent circuit of the matrix UPFC transmission system model. For system modeling, the power sources and the coupling transformers are all considered ideal.

Fig. 1. Transmission network with matrix converter UPFC.

Fig. 2. Three-phase equivalent circuit of the matrix UPFC and transmission line.

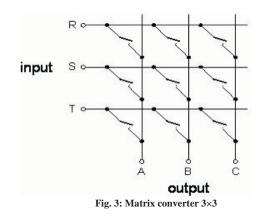

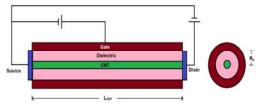

A matrix converter is a direct frequency changer. This converter consists of an array of  $n \times m$  bidirectional switches arranged so that any of the output lines of the converter can be connected to any of the input lines. The bidirectional switch is realized by using some semiconductor devices. They can be either discrete or integrated to the module. The bidirectional switch can be implemented in various ways. For the matrix converter, we chose modules which include 3 bidirectional switches in common emitter a configuration. The modulator is thus realized for these switchers.

The Matrix Converter is a single stage converter which has an array of  $m \times n$  bidirectional power switches to connect, directly, an m-phase voltage source to an n-phase load. The Matrix Converter of  $3 \times 3$  switches, shown in Figure 5, has the highest practical interest because it connects a three-phase voltage source with a three-phase load, typically a

motor. Normally, the matrix converter is fed by a voltage source and for this reason, and the input terminals should not be short-circuited.

On the other hand, the load has typically an inductive nature and for this reason an output phase must never be opened. Defining the switching function of a single switch as

$$Skj = \begin{cases} 1, Switch Skj closed \\ 0, Switch Skj open \end{cases}$$

$$k = \{A B C\} \qquad j = \{a b c\}$$

The constraints discussed above can be expressed by

$$SAj + SBj + SCj = 1$$

,  $j = \{a \ b \ c\}$

With these restrictions, the  $3 \times 3$  Matrix Converter has 27 possible switching states.

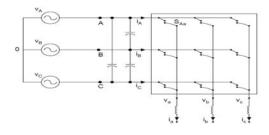

FIGURE 4: Simplified circuit of a 3×3 Matrix Converter.

The load and source voltages are referenced to the supply neutral, '0' in the Figure 4, and can be expressed as vectors defined by:

$$\mathbf{V}_{o} = \begin{bmatrix} \mathbf{V}_{a}(t) \\ \mathbf{V}_{b}(t) \\ \mathbf{V}_{c}(t) \end{bmatrix}, \quad \mathbf{V}_{i} = \begin{bmatrix} \mathbf{V}_{A}(t) \\ \mathbf{V}_{B}(t) \\ \mathbf{V}_{C}(t) \end{bmatrix}$$

The relationship between load and input voltages can be expressed as:

$$\begin{bmatrix} \mathbf{V}_{a}(t) \\ \mathbf{V}_{b}(t) \\ \mathbf{V}_{c}(t) \end{bmatrix} = \begin{bmatrix} \mathbf{S}_{Aa} & \mathbf{S}_{Ba} & \mathbf{S}_{Ca} \\ \mathbf{S}_{Ab} & \mathbf{S}_{Bb} & \mathbf{S}_{Cb} \\ \mathbf{S}_{Ac} & \mathbf{S}_{Bc} & \mathbf{S}_{Cc} \end{bmatrix} \begin{bmatrix} \mathbf{V}_{A}(t) \\ \mathbf{V}_{B}(t) \\ \mathbf{V}_{C}(t) \end{bmatrix}$$

$$Vo = T \times Vi$$

Where T is the instantaneous transfer matrix. In the same form, the following relationships are valid for the input and output currents:

| $\dot{\mathbf{i}}_{i} = \begin{bmatrix} \dot{\mathbf{i}}_{a} \begin{pmatrix} \mathbf{t} \\ \mathbf{i}_{b} \begin{pmatrix} \mathbf{t} \\ \mathbf{t} \\ \mathbf{i}_{c} \begin{pmatrix} \mathbf{t} \end{pmatrix} \end{bmatrix}$ | $\mathbf{i}_{0} = \begin{bmatrix} \mathbf{i}_{A}(t) \\ \mathbf{i}_{B}(t) \\ \mathbf{i}_{C}(t) \end{bmatrix}$ |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| $i_i = T^T \cdot io$                                                                                                                                                                                                         |                                                                                                              |  |

Where  $T_T$  is the transpose matrix of T.

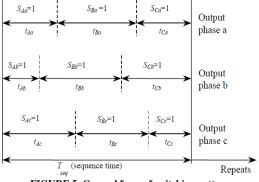

The above gives the instantaneous relationships between input and output quantities. To derive modulation rules, it is also necessary to consider the switching pattern that is employed. This typically follows a form similar to that shown in the Figure 5.

FIGURE 5: General form of switching pattern.

By considering that the bidirectional power switches work with high switching frequency, a low frequency output voltage of variable amplitude and frequency can be generated by modulating the duty cycle of the switches using their respective switching functions. Let  $M_{kj}(t)$  be the duty cycle of switch  $S_{kj}(t)$ , defined as  $M_{kj}(t) = t_{kj}/T_{seq}$ , which can have the following values:

The low-frequency transfer matrix is defined by

$$M(t) = \begin{bmatrix} M_{Aa} & M_{Ba} & M_{Ca} \\ M_{Ab} & M_{Bb} & M_{Cb} \\ M_{Ac} & M_{Bc} & M_{Cc} \end{bmatrix}$$

The low-frequency component of the output phase voltage is given by

$Vo(t) = M(t) \cdot Vi(t)$

The low-frequency component of the input current is  $i_i(t) = M(t)^T \cdot i_0(t)$

The Matrix Converter is a forced commutated converter which uses an array of controlled bidirectional switches as the main power elements to create a variable output voltage system with unrestricted frequency. It does not have any dc-link circuit and does not need any large energy storage elements. The matrix converter is an array of bidirectional switches as the main power elements, which interconnects directly the power supply to the load, without using any dc-link or large energy storage elements.

The most important characteristics of matrix converters are; 1) Simple and compact power circuit, 2) Generation of load voltage with

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

arbitrary amplitude and frequency, 3) Sinusoidal input and output currents, 4) Operation with unity power factor, 5) Regeneration capability.

These highly attractive characteristics are the reason for the tremendous interest in this topology. The key element in a matrix converter is the fully controlled four quadrant bidirectional switch, which allows high frequency operation. The early work dedicated to unrestricted frequency changers used thyristors with external forced commutation circuits to implement the bi-directional controlled switch. With this solution the power circuit was bulky and the performance was poor. The introduction of power transistors for implementing the bidirectional switches made the matrix converter topology more attractive. However, the real development of matrix converters starts with the work of Venturini and Alesina published in 1980. They presented the power circuit of the converter as a matrix of bi-directional power switches and they introduced the name "Matrix Converter." One of their main contributions is the development of a rigorous mathematical analysis to describe the low-frequency behavior of the converter, introducing the "low frequency modulation matrix" concept. In their modulation method, also known as the direct transfer function approach, the output voltages are obtained by the multiplication of the modulation (also called transfer) matrix with the input voltages.

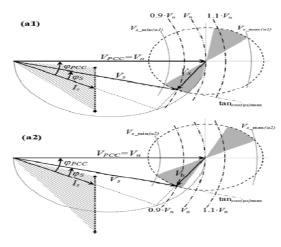

### **B. DIRECT POWER CONTROL OF MC-UPFC**

### I. Line Active and Reactive Power Sliding Surfaces

The DPC controllers for line power flow are here derived based on the sliding mode control theory. In steady state, V<sub>d</sub> is imposed by source Vs. The transmission-line currents can be considered as state variables with first-order dynamics dependent on the sources and time constant of impedance  $L_2/R_2$ . Therefore, transmission-line active and reactive powers present first-order dynamics and have a strong relative degree of one, since from the control viewpoint, its first time derivative already contains the control variable (the strong relative degree generally represents the number of times the control output variable must be differentiated until a control input appears explicitly in the dynamics). From the sliding mode control theory, robust sliding surfaces to control the P and Q variables with a relatively strong degree of one can be obtained considering proportionality to a linear combination of the errors of the state variables. Therefore, define the active power error  $e_p$  and the reactive power error  $e_q$  as the difference between the power references Pref, Qref and the actual transmitted powers P, Q, respectively.

$$e_P = P_{\text{ref}} - P$$

$$e_Q = Q_{\text{ref}} - Q.$$

Then, the robust sliding surfaces  $S_p(e_p, t)$  and  $S_Q(e_q, t)$  must be proportional to these errors, being zero after reaching sliding mode.

$$S_P(e_P, t) = k_P(P_{ref} - P) = 0$$

$$S_Q(e_Q, t) = k_Q(Q_{ref} - Q) = 0.$$

The proportional gains  $K_p$  and  $K_q$  are chosen to impose appropriate switching frequencies.

## II. Line Active and Reactive Power Direct Switching Laws:-

The DPC uses a nonlinear law, based on the errors  $e_p$  and  $e_q$  to select in real time the matrix converter switching states (vectors). Since there are no modulators and/or pole zero-based approaches, high control speed is possible. To guarantee stability for active power and reactive power controllers, the sliding-mode stability conditions must be verified

$$S_P(e_P, t) \overset{\bullet}{S}_P(e_P, t) < 0$$

$$S_Q(e_Q, t) \overset{\bullet}{S}_Q(e_Q, t) < 0.$$

To design the DPC control system, the six vectors will not be used, since they require extra algorithms to calculate their time-varying phase. The variable amplitude vectors, only the 12 highest amplitude voltage vectors are certain to be able to guarantee the previously discussed required levels of V<sub>Ld</sub> and V<sub>La</sub> needed to fulfill the reaching conditions. The lowest amplitude voltages vectors, or the three null vectors could be used for near zero errors. If the control errors ep and eo are quantized using two hysteresis comparators, each with three levels (-1, 0 and+1), nine output voltage error combinations are obtained. If a two-level comparator is used to control the shunt reactive power, as discussed in next subsection, 18 error combinations (9x2=18) will be defined, enabling the selection of 18 vectors. Since the three zero vectors have a minor influence on the shunt reactive power control, selecting one out 18 vectors is adequate. Using the same reasoning for the remaining eight active and reactive power error combinations and generalizing it for all other input voltage sectors, Table II is obtained. These P, Q controllers were designed based on control laws not dependent on system parameters, but only on the errors of the controlled output to ensure robustness to parameter variations or operating conditions and allow system order reduction, minimizing response times.

### III. DIRECT CONTROL OF MATRIX CONVERTERS INPUT REACTIVE POWER:-

In addition, the matrix converter UPFC can be controlled to ensure a minimum or a certain desired reactive power at the matrix converter input. Similar to the previous considerations, since the voltage source input filter dynamics has a strong relative degree of two, then a suitable sliding surface  $S_{Qi}(e_{qi},t)$  will be a linear combination of the desired reactive

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

power error  $e_{qi}=Q_{iref}-Q_i$  and its first-order time derivative.

$$S_{Q_i}(e_{Q_i}, t) = (Q_{i_{\text{ref}}} - Q_i) + K_{Q_i} \frac{d}{dt} (Q_{i_{\text{ref}}} - Q_i).$$

The time derivative can be approximated by a discrete time difference, as  $K_{Qi}$  has been chosen to obtain a suitable switching frequency, since as stated before, this sliding surface needs to be quantized only in two levels (-1 and+1 ) using one hysteresis comparator. To fulfill a stability condition similar to considering the input filter dynamics is obtained. **IV.IMPLEMENTATION OF THE DPC-MC AS UPFC**

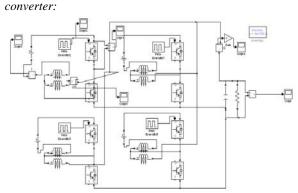

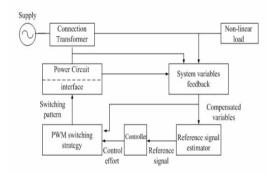

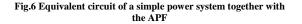

As shown in the block diagram (Fig. 6), the control of the instantaneous active and reactive powers requires the measurement of G<sub>S</sub> voltages and output currents necessary to calculate  $S_{\alpha}(e_{p},t)$  and sliding surfaces. The output currents  $S_{\beta}(e_0,t)$ measurement is also used to determine the location of the input currents q component. The control of the matrix converter input reactive power requires the input currents measurement to calculate  $S_{Oi}(e_{Oi},t)$ . At each time instant, the most suitable matrix vector is chosen upon the discrete values of the sliding surfaces, using tables derived from Tables I and II for all voltage sectors. These vectors do not produce significant effects on the line active and reactive power values, but the lowest amplitude voltage vectors have a high influence on the control of matrix reactive power.

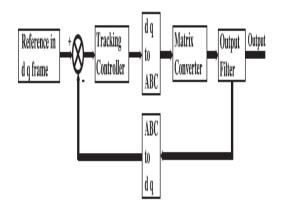

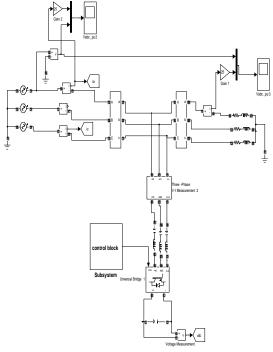

### A. Voltage Control in d-q Reference Frame

The output voltages are measured across the capacitors in the output filter and are then feedback separately to the system control. In the d-q reference frame the three- phase output voltages are transformed into two dc signals on the d and q axis. Using the designed tracking controller on each of the two axes, the presence of the interpreter will ensure a small steady state error on the voltage loop. The control signal in d-q frame are converted back to the ABC reference frame an applied to the modulator. These signal are the reference signal required by the modulator in order to produce the pulses needed to commutate the bi-directional switches. Figure 7 shows the control strategy in d-q reference frame.

Figure 7: Control strategy in d-q reference frame.

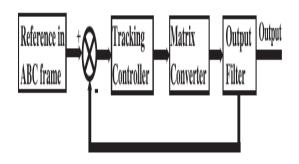

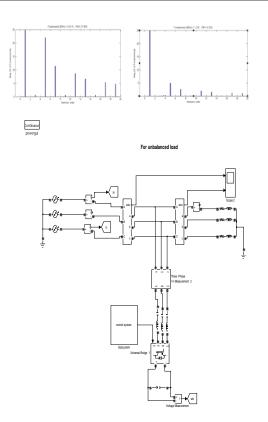

### **B.** Voltage Control in ABC Reference Frame

The problem presented in previous section when the Matrix Converter is connected to an unbalanced load can be solved using a control system working directly in the ABC reference frame. The reference signals which are a set of a three-phase rms voltages at 400Hz in the ABC frame are compared to the voltages measured across the output filter capacitors. The error signal obtained is then applied to the tracking controller on each phase. Each tracking controller generates a control signal which is applied directly to the modulator. Then the modulator produces the pulses required to commutate the bidirectional switches. The general scheme of the system used is shown in Figure 8. The procedure used to design the tracking controller of for the ABC reference is the same as the one used in the design of the tracking controller in the d-q reference frame. In this case because the gain is now set as 0.6. Since the reference of our control is a 400Hz three-phase signal, the interpreter present in the controller will not be able to achieve a small steady state error, being the all closed-loop system of a limited bandwidth. Therefore a gain has been introduced in order to compensate for the amplitude mismatch in the output. The value of this gain has been found to be 6 by trial and error. When the control system was design, the block representing the Matrix Converter was considered as a unity gain. In the practical implementation, the Matrix Converter consists of electronic components which have voltage drops and dissipate energy and therefore the Matrix Converter has a transfer function different from a unity gain. This modifies the closed loop considered in the design of the tracking controller. In the design of the controller, only the output filter has been considered as the plant. The Matrix Converter block is not considered as part of the closed loop. In practice, it have been found that the Matrix Converter can be replaced by a gain with a value between 5 and 6. Also, the block representing the Matrix Converter

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

introduces a delay. This delay can be compensated by the controller.

Figure 8: Control strategy in ABC reference frame.

### TABLE I STATE-SPACE VECTORS SELECTION, FOR INPUT VOLTAGES LOCATED AT SECTOR V<sub>i</sub> 1

|    |             |                               |                 |                 |                    |                 | Sec                | ctor           |               |                   |                    |                        |                |

|----|-------------|-------------------------------|-----------------|-----------------|--------------------|-----------------|--------------------|----------------|---------------|-------------------|--------------------|------------------------|----------------|

| Cα | $C_{\beta}$ | $I_{\theta}12$                | ; $I_{\theta}l$ | $I_{\theta}2$   | ; I <sub>0</sub> 3 | $I_04$          | ; I <sub>0</sub> 5 | $I_{\theta} 6$ | $I_{\theta}7$ | I <sub>0</sub> 8; | : I <sub>0</sub> 9 | $I_{\theta} 1 \theta;$ | $I_{\theta}11$ |

| Cα |             | $C_{\alpha} C_{\beta} C_{Qi}$ |                 | C <sub>Qi</sub> |                    | C <sub>Qi</sub> |                    | $C_{Qi}$       |               | $C_{Qi}$          |                    | C <sub>Qi</sub>        |                |

|    |             | +1                            | -1              | +1              | -1                 | +1              | -1                 | +1             | -1            | +1                | -1                 | +1                     | -1             |

| -1 | +1          | -9                            | +7              | -9              | +7                 | -9              | +7                 | +7             | -9            | +7                | -9                 | +7                     | -9             |

| -1 | 0           | +3                            | -1              | +3              | -1                 | -1              | +3                 | -1             | +3            | -1                | +3                 | +3                     | -1             |

| -1 | -1          | -6                            | +4              | +4              | -6                 | +4              | -6                 | +4             | -6            | -6                | +4                 | -6                     | +4             |

| 0  | +1          | -9                            | +7              | -9              | +7                 | -9              | +7                 | +7             | -9            | +7                | -9                 | +7                     | -9             |

| 0  | 0           | -2                            | +2              | +8              | -8                 | -5              | +5                 | +2             | -2            | -8                | +8                 | +5                     | -5             |

| 0  | -1          | -7                            | +9              | -7              | +9                 | -7              | +9                 | +9             | -7            | +9                | -7                 | +9                     | -7             |

| +1 | +1          | -4                            | +6              | +6              | -4                 | +6              | -4                 | +6             | -4            | -4                | +6                 | -4                     | +6             |

| +1 | 0           | +1                            | -3              | +1              | -3                 | -3              | +1                 | -3             | +1            | -3                | +1                 | +1                     | -3             |

| +1 | -1          | -7                            | +9              | -7              | +9                 | -7              | +9                 | +9             | -7            | +9                | -7                 | +9                     | -7             |

TABLE II STATE-SPACE VECTORS SELECTION FOR DIFFERENT ERROR COMBINATIONS

| Ca    | Сβ | Sector                           |                                   |                                  |                                  |                                   |                                   |  |  |  |

|-------|----|----------------------------------|-----------------------------------|----------------------------------|----------------------------------|-----------------------------------|-----------------------------------|--|--|--|

| ca cp |    | V <sub>i</sub> 12; 1             | V <sub>i</sub> 2;3                | V <sub>i</sub> 4;5               | Vi 6; 7                          | V <sub>i</sub> 8; 9               | V <sub>i</sub> 10; 11             |  |  |  |

| -1    | +1 | -9;+7                            | -9; +8                            | +8; -7                           | -7;+9                            | +9; -8                            | -8; +7                            |  |  |  |

| -1    | 0  | +3; -1                           | +3; -2                            | -2; +1                           | +1;-3                            | -3; +2                            | +2; -1                            |  |  |  |

| -1    | -1 | -6; +4                           | -6; +5                            | +5;-4                            | -4; +6                           | +6; -5                            | -5; +4                            |  |  |  |

| 0     | +1 | -9; +7; +6; -4                   | -9; +8; +6; -5                    | +8; -7; -5; +4                   | -7; +9; +4; -6                   | +9; -8; -6; +5                    | -8; +7; +5; -4                    |  |  |  |

| 0     | 0  | Za; Zb; Zc;<br>-8;+2;-5;+8;-2;+5 | Za; Zb; Zc;<br>-7;+1;-4; +7;-1;+4 | Za; Zb; Zc;<br>+9;-3;+6;-9;+3;-6 | Za; Zb; Zc;<br>-8;+2;-5;+8;-2;+5 | Za; Zb; Zc;<br>-7;+1;-4; +7;-1;+4 | Za; Zb; Zc;<br>-9;+3;-6; +9;-3;+6 |  |  |  |

| 0     | -1 | -6; +4; +9; -7                   | +5; -6; -8; +9                    | +5; -4; -8; +7                   | -4; +6; +7; -9                   | +6; -5; -9; +8                    | -5; +4; +8; -7                    |  |  |  |

| +1    | +1 | +6;-4                            | +6; -5                            | -5; +4                           | +4; -6                           | -6; +5                            | +5;-4                             |  |  |  |

| +1    | 0  | -3; +1                           | +2; -3                            | -1;+2                            | +3; -1                           | -2;+3                             | +1;-2                             |  |  |  |

| +1    | -1 | +9; -7                           | +9; -8                            | +7;-8                            | +7; -9                           | -9; +8                            | +8; -7                            |  |  |  |

Fig.6. Control scheme of direct power control of the threephase matrix converter operating as a UPFC.

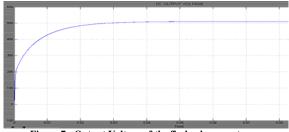

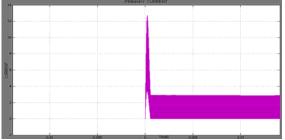

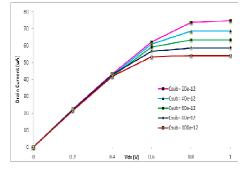

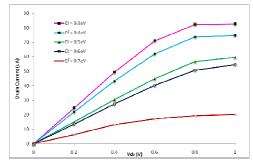

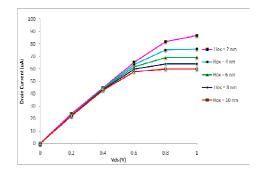

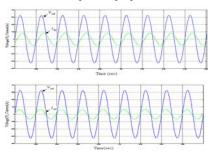

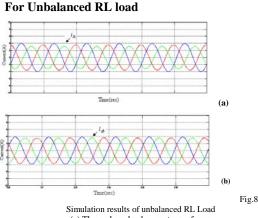

### **V. SIMULATION RESULTS**

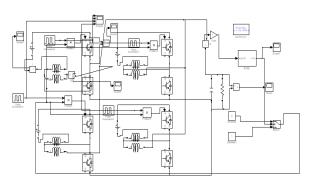

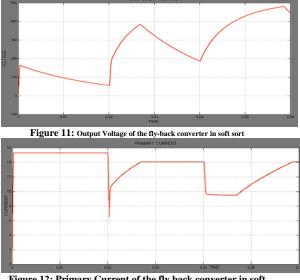

The performance of the proposed direct control system was evaluated with a detailed simulation model using the MATLAB/Simulink SimPowerSystems to represent the matrix converter, transformers, sources and transmission lines, and Simulink blocks to simulate the control system. Ideal switches were considered to simulate matrix converter semiconductors minimizing simulation times.

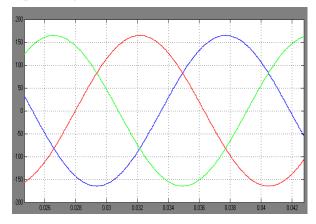

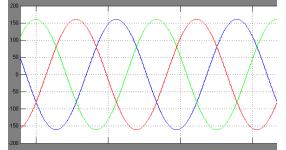

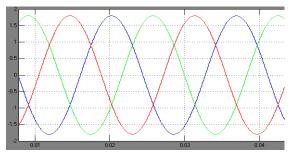

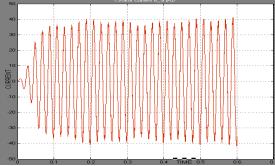

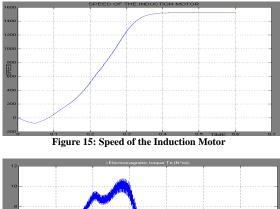

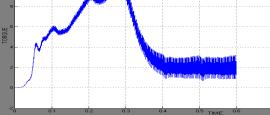

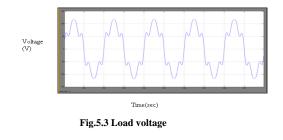

### Input voltage:-

### Advanced Direct Power Control Of Matrix Converter Based Unified Power-Flow Controller

### Input current:-

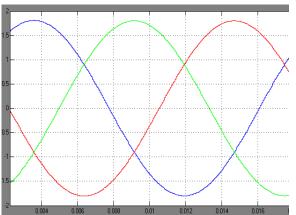

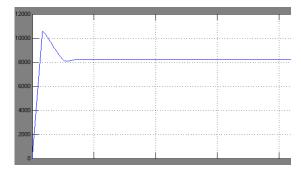

Line active power:-

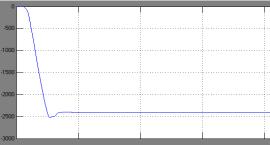

### Line reactive power:-

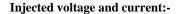

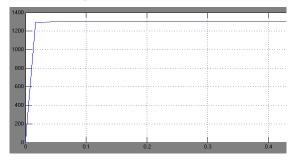

### Injected line reactive power:-

Injected line active power:-

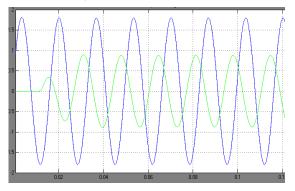

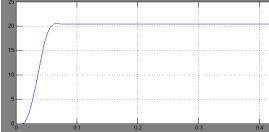

**Output voltage:-**

Output current:-

### VI. CONCLUSION

This paper derived advanced nonlinear direct power controllers, based on sliding mode control techniques, for matrix converters connected to power transmission lines as UPFCs. Presented simulation results show that active and reactive power flow can be advantageously controlled by using the proposed DPC. Results show no steadystate errors, no cross-coupling, insensitivity to nonmodeled dynamics and fast response times, thus confirming the expected performance of the presented

nonlinear DPC methodology. The obtained DPC-MC results were compared to PI linear active and reactive power controllers using a modified Venturini high-frequency PWM modulator. Despite showing a suitable dynamic response, the PI performance is inferior when compared to DPC. Furthermore, the PI controllers and modulator take longer times to compute. Obtained results show that DPC is a strong nonlinear control candidate for line active and reactive power flow. It ensures transmission-line power control as well as sending end reactive power or power factor control.

### REFERENCES

- School of Electrical and Electronic Engineering University Park Nottingham, NG72RD" Matrix Converters: A Technology Review" IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 49, NO. 2, APRIL 2002

- [2]. Fang Gao, Student Member, and M. Reza Iravani, Fellow, "Dynamic Model of a Space Vector Modulated Matrix Converter" IEEE TRANSACTIONS ON POWER DELIVERY, VOL. 22, NO. 3, JULY 2007

- [3]. C Watthanasam, L Zhang, D T W Liang "Analysis and DSPbased Implementation of a Modulation Algorithms for AC-AC Matrix Converters "Dept. of Electronic and, Electrical Engineering University of Bradford, Bradford, BD7 IDP, UK

- [4]. Carlos Ortega1, Antoni Arias, Xavier del Toro3, Emiliano Aldabas, Josep Balcells, "Novel Direct Torque Control for Induction Motors using short voltage vectors of Matrix Converters." MIEEE, 1, 2,3,4,5 Technical University of Catalonia. Electronics Engineering Dept. Colom 1, Terrassa 08222, Catalonia, Spain.

- [5]. Hong-Hee Lee, Hoang M. Nguyen, Eui-Heon Jung," A Study on Reduction of Common-Mode Voltage in Matrix Converter with Unity Input Power Factor and Sinusoidal Input/Output Waveforms." School of Electrical Engineering University of Ulsan Muger2Dong Nam-gu, Ulsan city Republic of Korea.

- [6]. Fan Yue, Patrick W. Wheeler, and Jon C. Clare,"Relationship of Modulation Schemes for Matrix Converters" School of Electrical & Electronic Engineering University of Nottingham, University Park Nottingham, NG7 2RD UK.

*K.Meenendranath Reddy was* born in Nandyal, A.P, India. He received the B.Tech (Electrical and Electronics Engineering) degree from the madina engineering college, kadapa in 2010: and Pursuing M.Tech (Electrical Power Systems) from

the Annamacharya Institute of Technology and Science, rajampeta.

e-mail: kaipa.meenendranathreddy@gmail.com

**O.Hemakesavulu was** born in Kadapa, A.P, India. He received M.Tech (Power Electronics) degree from Rajeev Gadhi Memorial College of Engineering & Technology, Nandyal And BTech (Electrical

and Electronics Engineering) from Annamacharya Institute of Technology and Sciences,Rajampet.Presently pursuing Ph.D. email: hkesavulu <u>6@gmail.com</u>

M. Padma Lalitha. is awarded Ph.D for her work "Soft Computing Techniques for optimal DG placement in Radial Distribution System "from S.V.U. in the year 2011and is a graduate

from JNTU, Anathapur in Electrical & Electronics Engineering in the year 1994. Obtained Post graduate degree in PSOC from S.V.U, Tirupathi in the year 2002. Having 14 years of experience in teaching in graduate and post graduate level. Presently working as Professor and HOD of EEE department in AITS, Rajampet

e-mail: padmalaitha mareddy @yahoo.co.in

**~~**

### SUBSTATION MONITORING AND CONTROL USING GSM TECHNOLOGY

### <sup>1</sup>V. BHASKAR & <sup>2</sup>T. GOWRI MANOHAR

<sup>1</sup>Department of E.E.E., Srikalahasteeswara Institute of Technology, Srikalahasti, A.P., India, <sup>2</sup>Department of E.E.E., S.V. University, Tirupati, A.P., India.

**Abstract:** The purpose of this project is to acquire the remote electrical parameters like Voltage, Current and Frequency and send these real time values over GSM network using GSM Modem/phone along with temperature at power station. This project is also designed to protect the electrical circuitry by operating an Electromagnetic Relay. This Relay gets activated whenever the electrical parameters exceed the predefined values. The Relay can be used to operate a Circuit Breaker to switch off the main electrical supply. User can send commands in the form of SMS messages to read the remote electrical parameter. This system also can automatically send the real time electrical parameters periodically (based on time settings) in the form of SMS. This system can be designed to send SMS alerts whenever the Circuit Breaker trips or whenever the Voltage or Current exceeds the predefined limits. This project makes use of an onboard computer which is commonly termed as microcontroller. This onboard computer can efficiently communicate with the different sensors being used. The controller is provided with some internal memory to hold the code. This memory is used to dump some set of assembly instructions into the controller. And the functioning of the controller is dependent on these assembly instructions. The controller is programmed using Embedded C language.

*Keyword:* GSM Modem, Key words - Short Message Service (SMS), Global Systems for Mobile Communication (GSM), AT Command, GSM Modem, relay, circuit breaker (C.B)

### I. INTRODUCTION

Electricity is an extremely handy and useful form of energy. It plays an ever growing role in our modern industrialized society. The electrical power systems are highly non-linear, extremely huge and complex networks. Such electric power systems are unified for economical benefits, increased reliability and operational advantages. They are one of the most significant elements of both national and global infrastructure, and when these systems collapse it leads to major direct and indirect impacts on the economy and national security. A power system consists of components such as generators, lines, transformers, loads, switches and compensators. However, a widely dispersed power sources

And loads are the general configuration of modern power systems. Electric power systems can be divided into two sub-systems, namely, transmission systems and distribution systems. The main process of a transmission system is to transfer electric power from electric generators to customer area, whereas a distribution system provides an ultimate link between high voltage transmission systems and consumer services. In other words, the power is distributed to different customers from the distribution system through feeders, distributors and service mains. Supplying electricity to consumers necessitates power generation, transmission, and distribution. Initially electric power is generated by using electric generators such as: nuclear power generators, thermal power generators and hydraulic power generators and then transmitted through transmission systems using high voltage. Power departs from the generator and enters into a transmission substation, where huge

transformers convert the generator's voltage to extremely high voltages (155kV to 765 kV) for longdistance (up to about 300 miles) transmission. Then, the voltage level is reduced using transformers and power is transferred to customers through electric power distribution systems. Power starts from the transmission grid at distribution substations where the voltage is stepped-down (typically to less than 10kV) and carried by smaller distribution lines to supply commercial, residential, and industrial users. Novel electric power systems encompassing of power transmission and distribution grids consist of copious number of distributed, autonomously managed, capital-intensive assets. Such assets comprise: 1.) power plants, 2.) transmission lines, 3.) transformers, and 4.) protection equipment.

Electric utility substations are used in both the transmission and distribution system and operate independently to generate the electricity. A typical substation facility consists of a small building with a fenced-in yard that contains transformers, switches, voltage regulators, and metering equipment that are used to adjust voltages and monitor circuits. A reliable and efficient process of these networks alone is not very significant when these electricity systems are pressed to their parameters of its performance, but also under regular operating conditions. Generators and loads are some components that coerce the continuous dynamic behaviour. The distance between the Generators and loads may be in terms of hundreds of miles. Hence, the amount of huge power exchanges over long distances has turned out as a result of the lack of quality of the electric power. During the earlier development stages the issues on

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

quality of power were not frequently reported. Quality of supply is a mixture of both voltage quality and the non-technical features of the interaction from the power network to its customers. Demanding the quantity of power being delivered at the user side has raised the alarm due to the increase in demand of electricity in the customer's side. The power generated at the main stations is transported hundreds of miles using transmission lines before they reach the substations. A huge amount of power is lost during the transportation of the generated power which leads to the reduction in the quantity of power received at the substations. Also the electric lines users have identified that the number of drawbacks caused by electrical power quality variations are increasing rapidly.

These variations have already existed on electrical systems, but recently they are causing serious problems. Therefore, measurements must be acquired either from one end or from both the ends of a faulted line. Only meager recorded data is available at limited substation locations in certain systems.

When a fault occurs in such systems, only a few (two or three) recording devices are triggered. The most likely case is that the measurements could not be obtained at either or both ends of the faulted transmission line leads to drop in the quality of the power.

To improve the quality of power with sufficient solutions, it is necessary to be familiar with what sort of constraint has occurred. Additionally, if there is any inadequacy in the protection, monitoring and control of a power system, the system might become unstable. Therefore, it necessitates a monitoring system that is able to automatically detect, monitor, typify and classify the existing constraints on electrical lines. This brings up advantages to both end users and utility companies.

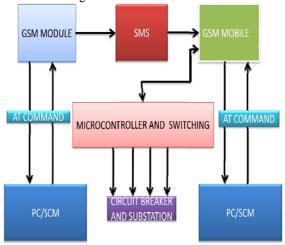

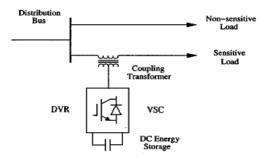

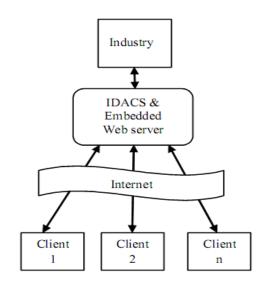

### II SYSTEMS COMMUNICATION ARCHITECTURE

As shown in Figure 1 the wireless transference of Monitoring and Control using GSM Technology in this paper is built on the SMS of the GSM network. Data messages produced at one end of the monitoring system are encapsulated into a short message by the gateway and sent to remote monitoring devices at another end. When a short message is received, it can be restored to its original industrial form by removing the SMS PDU head.

This is also conducted by the gateway of the monitoring system. If needed, the message content can be put into other form and forwarded by the gateway through other industrial net work. Since the transference is a trans-network task, gateways are required to perform protocol conversion along with other functions. The system makes use of the routing function of the GSM network to deliver a message to another gateway. This is not only controlling and also monitoring 33kv/11kv either step-up or step- down substation.

Fig. 1: System Communication Architecture

### III. WORKI NG

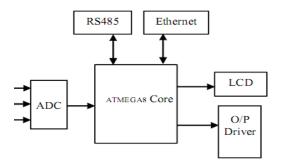

In this project we are using the GSM technology. A micro controller (also micro controller u nit, MCU or  $\mu$ C) is a small computer on a single integrated circuit consisting of a relatively simple CPU combined with support functions such as a crystal oscillator, timers and etc. Microcontrollers are used in automatically controlled products and devices such a s automobile engine control systems, remote controls, office machines, appliances, power tools and toys. The LCD will give the professional look for the project. It also displays the current operation of the system. The micro controller is used to control the relay drivers depending upon the soft ware program. Major role of this project is to receive the SMS to relay and send the signal to circuit breaker in a substation Initially the SMS is received from the person authorized to use this setup (destination) by the GSM modem (SIM300 MODEM) & is transferred to the microcontroller r devices kit with the help of a MAX 232 chip. As per the AT commands given by the microcontroller to the modem, the control signal from

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

the SMS is extracted and is used to control the devices connected to it. We have to convert the 'septets' of the to phone to 'octets' because the microcontroller need bytes with 8 bits length ( The 'septet' is 1 byte with 7 bits length and 'octet' is 1 byte with 8 b its length). All this process is necessary t o decode the message from SMS.

A program (for extracting the control signal part from received SMS) is loaded into microcontroller devices kit, and then the circuit is connected to the modem. The microcontroller now tries to read the SMS from t he 1st memory location of the modem and it keeps trying again until the modem receives any (programmed for every one second). Before implementing the control signal part of t he SMS, the modem extracts the number from the SM S and verifies if this number has the access to control the device or not. For controlling the device s, the message will be sent in hexa decimal format. The hex data is converted to the equivalent binary and the particular output is enabled. For example if the message is "AB" the equivalent binary is "10101011" this implies that the output 1, 3, 5, 7, 8 are enabled and the remaining ports are disabled. We have connected LEDs to the ports of micro controller to show the output and their status indicates whether the ports are set to 'ON' or 'OFF'. And substation control and monitoring like send the message in text format like SUBSTATION 10N and SUBSTATION 20N and SUBSTATION 10FF and SUBSTATION 20FF.

### **IV. COMPONENTS USED**

Power Supply: 5v and 3.6v and 4.6v, 12v DC Micro controller: Philips P89V51RD2-8bit. LCD: 16x2 characters RS 232 converter: MAX 232 Flash Magic: Vision 2.4 Keil-C m-vision: µVision3 (IDE -Version)

### V . GSM COMMANDS

Commands always start with AT (which means Attention) and finish with a <CR> character. Information responses and result codes, Responses start and end with <CR><LF>, except for the ATV0 DCE response format) and the ATQ1 (result code suppression) commands.

If command syntax is incorrect, an ERROR string is returned.

If command syntax is correct but with some incorrect parameters, the +CME ERROR:

<Err> or +CMS ERROR: <sms Err> strings are returned with different error codes.

If the command line has been performed successfully, an OK string is returned.

In some cases, such as "AT+CPIN?" or (unsolicited) incoming events, the product does not return the OK string as a response.

In the following examples <CR> and <CR><LF> are intentionally omitted.

1. Manufacturer identification +CGMI

2. Request model identification +CGMM

3. Request revision identification +CGMR

4. Product Serial Number +CGSN

Preferred Message Format +CMGF

Description: The message formats supported are text mode and PDU mode. In PDU mode, a complete SMS Message including all header information is given as a binary string (in hexadecimal format). Therefore, only the following set of characters is allowed:

$\{ ,0 \ ,\ 1 \ ,\ 2 \ ,\ 3 \ ,\ 4 \ ,\ 5 \ ,\ 6 \ ,\ 7 \ ,\ 8 \ , \\ 9 \ , M \ , M \ , M \ , C \ ,\ D \ ,\ E \ ,\ F \ \}. \ Each \ pair$ or characters are converted to a byte (e.g.: "41 is converted to the ASCII character "A , whose ASCII code is 0x41 or 65). In Text mode, all commands and responses are in ASCII characters. The format selected is stored in EEPROM by the +CSAS command.

Command syntax: AT+CMGF

Read message +CMGR

Description: This command allows the application to read stored messages. The messages are read from the memory selected by +CPMS command.

Command syntax: AT+CMGR=<index>

Send message +CMGS

Description: The <address> field is the address of the terminal to which the message is sent. To send the message, simply type, <ctrl-Z> character (ASCII 26). The text can contain all existing characters except <ctrl-Z> and <ESC>(ASCII 27).This command can be aborted using the <ESC> character when entering text. In PDU mode, on hexadecimal characters are used

("0 ... 9 , A ... F ). Syntax: AT+CMGS= <length> <CR> PDU is entered <ctrl-Z / ESC >.

#### VI .MICROCONTROLLER

Description: The 89C51RB2/RC2/RD2 device contains a non-volatile 16kB/32kB/64kB Flash program memory that is both parallel programmable serial In-System and In-Application and Programmable.

In-System Programming (ISP) allows the user to download new code while the microcontroller sits in the application. In-Application Programming (IAP) means that the microcontroller fetches new program code and reprograms itself while in the system. This allows for remote programming over a modem link. A default serial loader (boot loader) program in ROM allows serial In-System programming of the Flash memory via the UART without the need for a loader in the Flash code. For In Application Programming, the user program erases and reprograms the Flash

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

memory by use of standard routines contained in ROM. This device executes one machine cycle in 6 clock cycles, hence providing twice the speed of a conventional 80C51.

This device is a Single-Chip 8-Bit Microcontroller manufactured in advanced CMOS process and is a derivative of the 80C51 microcontroller family. The device also has four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, and four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits.

The added feature of the P89C51RB2/RC2/RD2 makes it a powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control.

### VII . A DEVELOPMENT TOOLS

Keil ( $\mu$ Vision 2): The Keil C51 Cross Compiler is an ANSI C Compiler that is written specifically to generate fast, compact code for the 8051 microcontroller family. The C51 Compiler generates object code that matches the efficiency and speed of assembly programming. Using a high-level language like C has many advantages over assembly language *programming:*

• Knowledge of the processor instruction set is not required. Rudimentary knowledge of the memory structure of the 8051 CPU is desirable (but not necessary).

• Details like register allocation and addressing of the various memory types and data types is managed by the compiler.

• Programs get a formal structure (which is imposed by the C programming language) and can be divided into separate functions. This contributes to source code reusability as well as better overall application structure.

• The ability to combine variable selection with specific operations improves program readability.

• Keywords and operational functions that more nearly resemble the human thought process may be used.

• Programming and program test time is drastically reduced.

• The C run-time library contains many standard routines such as: formatted output, numeric conversions, and floating-point arithmetic.

• Existing program parts can be more easily included into new programs because of modular program construction techniques.

• The language C is a very portable language (based on the ANSI standard) that enjoys wide popular support and is easily obtained for most systems.

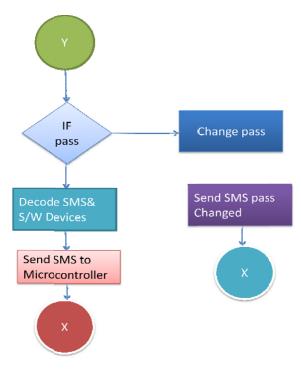

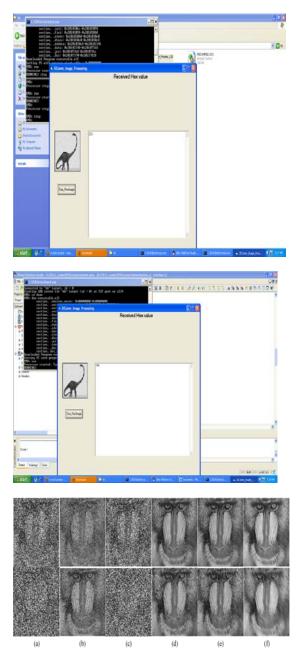

### VIII . FLOW CHART AND SOFTWARE IMPLEMENTATION

Software development: The software for the system is developed in Embedded C and Visual Basic. The flowcharts depicting the monitoring and control the different voltage level of substations and also control the circuit breaker is shown in fig2.

Fig. 8: Software Implementation

### IX .FLOW CHART

### X . CONCLUSION

The project "SUBSTATION MONITORING AND CONTROL USING GSM TECHNOLOGY" was designed such that the devices can be monitored and also controlled from anywhere in the world using GSM modem connected to mobile phone Integrating features of all the hardware components used have been developed in it. Presence of every module has been reasoned out and placed carefully, thus contributing to the best working of the unit. Secondly, using highly advanced IC s with the help of growing technology, the project has been successfully implemented. Thus the project has been successfully designed and tested.

### **REFERENCES:**

- Jyotishman Pathak, Yuan Li, Vasant Honavar and James D. McCalley, "A Service-Oriented Architecture for Electric Power Transmission System Asset Management", In ICSOC Workshops, pp: 26-37, 2006.

- [2]. B. A. Carreras, V. E. Lynch, D. E. Newman and I. Dobson, "Blackout Mitigation Assessment in Power Transmission Systems", Hawaii International Conference on System Science, January 2003.

- [3]. Xiaomeng Li and Ganesh K. Venayagamoorthy, "A Neural Network Based Wide Area Monitor for a Power System",

*IEEE Power Engineering Society General Meeting*, Vol. 2, pp: 1455-1460, 2005.

- [4]. Argonne National Laboratory, "Assessment of the Potential Costs and Energy Impacts of Spill Prevention, Control, and Countermeasure equirements for Electric Utility Substations", Draft Energy Impact Issue Paper, 2006.

- [5]. Gsm based Motor monitoring and speed control by V.Bhaskar International Journal of Mechanical and Industrial Engineering (IJMIE), ISSN No. 2231 –6477, Volume-1, Issue-2, 2011

- [6]. Daponte, M. Di Penta and G.Mercurio, "TRANSIENTMETER: A Distributed Measurement System for Power Quality Monitoring", *IEEE Transactions on Power Delivery*, Vol. 19, Issue. 2, pp: 456-463, 2004.

- [7]. G. Pudlo, S. Tenbohlen, M. Linders and G. Krost, "Integration of Power Transformer Monitoring and Overload Calculation into the Power System Control Surface", *IEEE/PES Transmission and Distribution Conference and Exhibition*, Vol. 1, pp: 470-474 Asia Pacific, 2002.

- [8]. Zhi-Hua Zhou, Yuan Jiang, Xu-Ri Yin, and Shi-Fu Chen, "The Application of Visualization and Neural Network Techniques in a Power Transformer Condition Monitoring System", In: T. Hendtlass and M. Ali eds. Lecture Notes in Artificial Intelligence 2358, Berlin: Springer- Verlag, pp: 325-334, 2002.

$\otimes$

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

## AN FPGA IMPLEMENTATION OF MODIFIED DECISION BASED UNSYMMETRICAL TRIMMED MEDIAN FILTER FOR THE REMOVAL OF SALT AND PEPPER NOISE IN DIGITAL IMAGES

### CHAITANYA BETHINA & M.PREMKUMAR

Department of Electronics and Communications, Shri Vishnu Engineering College for Women, Bhimavaram, India

Abstract- A modified decision based unsymmetrical trimmed median filter algorithm for the restoration of gray scale, and color images that are highly corrupted by salt and pepper noise is proposed in this paper. Images are often corrupted by impulse noise during acquisition and transmission; thus, an efficient noise suppression technique is required before subsequent image processing operations. Median filter (MF) is widely used in noise removal methods due to its denoising capability and computational efficiency. However, it is effective only for low noise densities. Extensive experimental results demonstrate that our method can obtain better performances in terms of both subjective and objective evaluations than denoising techniques. Especially, the proposed method can preserve edges very well while removing salt and pepper noise. Modified Decision Based Algorithm (MDBA), and Progressive Switched Median Filter (PSMF) shows better results at low and medium noise densities. At high noise densities, their performance is poor. A new algorithm to remove high-density salt and pepper noise using modified Decision Based Unsymmetric Trimmed Median Filter (DBUTMF) is proposed. The proposed algorithm replaces the noisy pixel by trimmed median. Since our algorithm is algorithmically simple, it is very suitable to be applied to many real-time applications and higher noise densities. When all the pixel values are 0's and 255's then the noise pixel is replaced by mean value of all the elements present in the selected window. The proposed algorithm is tested against different grayscale and color images and it gives better Peak Signal-to-Noise Ratio (PSNR) and Image Enhancement Factor (IEF).

Index Terms--Median filter, salt and pepper noise, unsymmetrical trimmed median filter

### I. INTRODUCTION

Images are often corrupted by salt and pepper noise due to error in transmission of digital images. There are two types of impulse noise, they are salt and pepper noise and random valued noise. Salt and pepper noise can corrupt the images where the corrupted pixel takes either maximum or minimum gray level. The objective of noise removal is to eliminate the salt and pepper noise with minimum deformation caused to the image. The new algorithm has lower computation time when compared to other standard algorithms. Results of the algorithm is compared with various existing algorithms and it is proved that the new method has better visual appearance and quantitative measures at higher noise densities In this standard median filter will be effective only at low noise densities. The standard median (SM) filter is a simple nonlinear smoother that can suppress noise while retaining sharp sustained changes (edges) in signal values. It particularly effective in reducing is impulsive-type noise. In An adaptive median

filter (AMF). The nonlinear mean filter cannot remove such positive and negative impulses simultaneously many switched median filters were proposed to detect and correct only the corrupted pixel. But at high noise densities the window size has to be increased which may lead to blurring the image. In switching median filter the major drawback is defining that a robust decision is difficult. Especially when the noise level is high.

× To overcome the above drawback, Decision Based Algorithm (DBA) is proposed. In this, image is denoised by using a 3\*3 window. Decision-based median filtering algorithm in which local image structures are used to estimate the original values of the noisy pixels.

In such case, neigh- boring pixel is used for replacement. This repeated replacement of neighboring pixel produces streaking effect. In order to avoid this drawback, Decision Based Unsymmetric Trimmed Median Filter (DBUTMF) is proposed. In case if the selected window contains all the values as 0 s and 255 s

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

means then trimmed median value cannot be obtained, so this is also not an effective one. Due to these the algorithm does not give better results at very high noise density that is at 80% to 90.Due to this the proposed Modified Decision Based Un- symmetric Trimmed Median Filter (MDBUTMF) algorithm re- moves this drawback at high noise density and gives better Peak Signalto-Noise Ratio (PSNR) and Image Enhancement Factor (IEF) values than the existing algorithm.

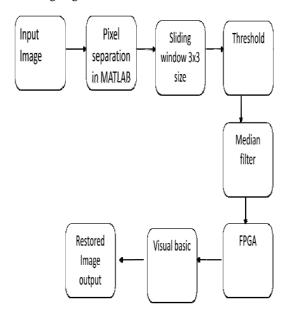

The above block diagram mainly consists of taking at 256/256 image and adding noise to it and converting a noise image into a matrix and then dividing a entire matrix into  $3 \times 3$  siding window, after dividing that window the sliding window is applied with our MDBUTMF to eliminate the noise pixel. This is represented as 0 and 255 after the eliminating noise pixel by images convert into text format. The text format is converted into bit stream. which is compatible to a FPGA kit is used by Spartan 3E which consist of micro blaze processor which is 32 bit processor consisting of RISC(Reduced Instruction Set) architecture. The output of FPGA kit is visualized in visual basic where the noise less image is retrieved.

A brief introduction of unsymmetric trimmed median filter is given in Section II. Section III describes about the proposed algorithm and different cases of proposed algorithm. The detailed description of the proposed algorithm with an example is presented in Section IV. Simulation results with different images are presented in Section V. Finally conclusions are drawn in Section VI.

## II. UNSYMMETRIC TRIMMED MEDIAN FILTER

The idex behind a trimmed filter is to reject the noisy pixel from the selected 3\*3 window. Alpha Trimmed Mean Filtering (ATMF) is a symmetrical filter where the trimming is symmetric at either end. A fixed impulse noise detector using unsymmetrical trimmed variants for the removal of high density salt and pepper noise for corrupted gray scale image is proposed. The proposed algorithm utilizes an impulse detector based on the threshold value obtained by unsymmetrical trimmed variants to check, if the pixel is noisy or not. In this median value is used to replace the noisy pixel. This filter is called trimmed median filter because the pixel values 0's and 255's are removed from the selected window. For high noise densities it does not preserve the image information due to the elimination of outlier values. Unsymmetrical trimmed filter replaced the symmetrical counterpart. The trimming was not uniform as in the previous case; So for the removal of salt and pepper noise at high noise densities with edge preservation (MDBUTMF) Modified decision based unsymmetrical trimmed median filter is proposed.

### III. PROPOSED ALGORITHM

The proposed Modified Decision Based Unsymmetric Trimmed Median Filter (MDBUTMF) and Salt and Pepper Noise Reduction Method avoid the above drawback even at high noise densities. The proposed method provides better Peak Signal-to-Noise Ratio (PSNR) than the existing methods. The proposed filter (MDBUTMF) replaces the noisy pixel by trimmed median value when some of the elements with values 0 s and 255 s are present in the selected window. If all the pixel values in the selected window are 0 s and 255 s means then the noisy pixel is replaced by mean value of all the elements present in that selected window. The throughput of MDBUTMF is a noise removal image. That is, if the processing pixel lies between maximum and minimum gray level values then it is noise free pixel, it is left unchanged. If the processing pixel takes the maximum or minimum gray level then it is noisy pixel which is processed by MDBUTMF. The steps of the MDBUTMF are elucidated as follows

An FPGA implementation of modified decision based unsymmetrical trimmed median filter for the removal of salt and pepper noise in digital images

**Step 1**: Select 2-D window of size 3×3. Assume that the pixel being processed is Pij.

Step 2: If 0 < Pij < 255 then Pij is an uncorrupted pixel and its value is left unchanged. This is illustrated in Case iii) of Section IV.

Step 3: If Pij=0 or Pij=255 then Pij is a corrupted pixel then two cases are possible as given in Case i) and ii).

Case i): If the selected window contains all the elements as 0's and 255's. Then replace Pij with the mean of the element of window.

Case ii): If the selected window contains not all elements as 0's and 255's. Then eliminate 255's and 0's and find the median value of the remaining elements. Replace Pij with the median value.

Step 4: Repeat steps 1 to 3 until all the pixels in the entire image are processed.

The pictorial representation of each case of the proposed algorithm is shown in Fig. 1.

The detailed description of each case of the flow chart shown in Fig. 1 is illustrated through an example in Section IV.

### IV. ILLUSTRATION OF MDBUTMF ALGORITHM

Each and every pixel of the image is checked for the presence of salt and pepper noise. Different cases are illustrated in this Section. If the processing pixel is noisy and all other pixel values are either 0's or 255's is illustrated in Case i). If the processing pixel is noisy pixel that is 0 or 255 is illustrated in Case ii). If the processing pixel is not noisy pixel and its value lies between 0 and 255 is illustrated in Case iii).

Case i) if the selected window contains salt/pepper noise as processing pixel (i.e., 255/0 pixel value) and neighboring pixel values contains all pixels that adds salt and pepper noise to the image:

$$\left(\begin{array}{cccc}

0 & 255 & 0 \\

0 & <255 > 0 \\

255 & 0 & 255

\end{array}\right)$$

Fig 1. Flow chart of MDBUTMF.

Since all the elements surrounding (Pij) are O's and 255's. If one takes the median value it will be either 0 or 255 which is again noisy. To solve this problem, the mean of the selected window is found and the processing pixel is replaced by the mean value. Here the mean value is 170. Replace the processing pixel by 170.

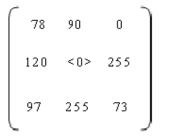

Case ii): If the selected window contains salt or pepper noise as processing pixel (i.e., 255/0 pixel value) and neighboring pixel values contains some pixels that adds salt (i.e., 255 pixel value) and pepper noise to the image:

Where "0" is processing pixel, i.e.,(Pij).

Now eliminate the salt and pepper noise from the selected window. That is, elimination of 0's and 255's. The 1-D array of the above matrix is [78 90 0 120 0 255 97 255 73]. After elimination of 0's and 255's the pixel values in the selected window will be [78 90

Where "255" is processing pixel, i.e.,

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

An FPGA implementation of modified decision based unsymmetrical trimmed median filter for the removal of salt and pepper noise in digital images

120 97 73]. Here the median value is 90. Hence replace the processing pixel Pij by 90. Case iii): If the selected window contains a noise free pixel as a processing pixel, it does not require further processing. For example, if the processing pixel is 90 then it is noise free pixel:

Where "90" is processing pixel, i.e.,(Pij).Since "90" is a noise free pixel it does not require further processing.

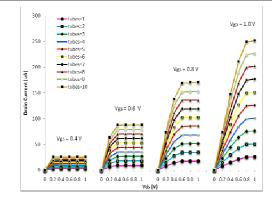

### **V. SIMULATION RESULTS**

The performance of the proposed algorithm is tested with different gray scale and color images. The noise density (intensity) is varied from 10% to 90%. For implementing our algorithm, we have used MATLAB 7 on a 2.80 GHz Pentium R processor with 1 GB of RAM. The performances of the proposed algorithm are quantitatively measured by the Peak Signal to Noise Ratio (PSNR) and Image Enhancement Factor (IEF as defined in (1) and (3), respectively:

| Noise | PSNR in dB |       |       |       |       |         |  |  |  |

|-------|------------|-------|-------|-------|-------|---------|--|--|--|

| in %  | MF         | AMF   | PSMF  | DBA   | MDBA  | MDBUTMF |  |  |  |

| 10    | 26.34      | 28.43 | 30.22 | 36.4  | 36.94 | 37.91   |  |  |  |

| 20    | 25.66      | 27.40 | 28.39 | 32.9  | 32.69 | 34.78   |  |  |  |

| 30    | 21.86      | 26.11 | 25.52 | 30.15 | 30.41 | 32.29   |  |  |  |

| 40    | 18.21      | 24.40 | 22.49 | 28.49 | 28.49 | 30.32   |  |  |  |

| 50    | 15.04      | 23.36 | 19.13 | 26.41 | 26.52 | 28.18   |  |  |  |

| 60    | 11.08      | 20.60 | 12.10 | 24.83 | 24.41 | 26.43   |  |  |  |

| 70    | 9.93       | 15.25 | 9.84  | 22.64 | 22.47 | 24.30   |  |  |  |

| 80    | 8.68       | 10.31 | 8.02  | 20.32 | 20.44 | 21.70   |  |  |  |

| 90    | 6.65       | 7.93  | 6.57  | 17.14 | 17.56 | 18.40   |  |  |  |

TABLE II COMPARISON OF IEF VALUES OF DIFFERENT ALGORITHMS FOR LENA IMAGE AT DIFFERENT NOISE DENSITIES

| DENSITIES |           |          |          |  |  |  |  |  |

|-----------|-----------|----------|----------|--|--|--|--|--|

|           | Media     | Switchin | MDBUTM   |  |  |  |  |  |

| Noise     | n Filter  | g        | F        |  |  |  |  |  |

| Densit    |           | Median   |          |  |  |  |  |  |

| у         |           | Filter   |          |  |  |  |  |  |

| 1%        | 42.105    | 36.579   | 51.4779  |  |  |  |  |  |

| 2%        | 40.152    | 36.2234  | 46.53315 |  |  |  |  |  |

|           | 8         |          |          |  |  |  |  |  |

| 3%        | 39.293    | 35.7106  | 46.1503  |  |  |  |  |  |

| 4%        | 8         | 35.2816  | 43.8922  |  |  |  |  |  |

| 5%        | 38.131    | 34.8293  | 41.9527  |  |  |  |  |  |

| MSE       | 2         |          |          |  |  |  |  |  |

|           | 37.473    |          |          |  |  |  |  |  |

|           | 7         |          |          |  |  |  |  |  |

| 1%        | 4.0042    | 14.2945  | 0.4626   |  |  |  |  |  |

| 2%        | 6.2776    | 15.5146  | 1.4437   |  |  |  |  |  |

| 3%        | 7.6506    | 17.4589  | 1.5779   |  |  |  |  |  |

| 4%        | 9.06      | 19.2718  | 2.65378  |  |  |  |  |  |

| 5%        | 5% 11.633 |          | 4.14771  |  |  |  |  |  |

|           | 6         |          |          |  |  |  |  |  |

|           |           |          |          |  |  |  |  |  |

PSNR in dB=

$$10 \log 10(\frac{255^2}{MSE})$$

$MSE = \sum_i \sum_j (Y(i,j) - \dot{Y}(i,j))^2 / M \times N$

$$IEF = \frac{\sum_{i} \sum_{j} (\eta(i,j) - y_{(i,j)})^{2}}{\sum_{i} \sum_{j} (\hat{y}(i,j) - y_{(i,j)})^{2}}$$

Where MSE stands for mean square error, IEF stands for image enhancement factor, is size of the image, Y represents the original image, denotes the denoised image, and represents the noisy image.

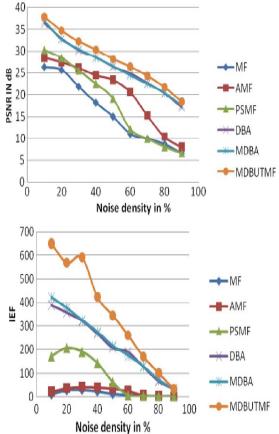

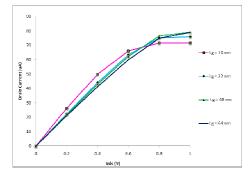

The PSNR and IEF values of the proposed algorithm are compared against the existing algorithms by varying the noise density from 10% to 90% and are shown in Table I and Table II. From the Tables I and II, it is observed that the performance of the proposed algorithm (MDBUTMF) is better than the existing algorithms at both low and high noise densities. A plot of PSNR and IEF against noise densities for Lena image is shown in Fig. 2.

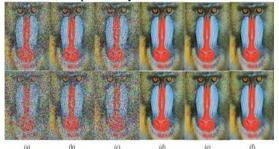

The qualitative analysis of the proposed algorithm against the existing algorithms at different noise densities for Baboon image is shown in Fig. 3. In this figure, the first column represents the processed image using MF at 80% and 90% noise densities. Subsequent columns represent the processed images for AMF, PSMF, DBA, MDBA and MDBUTMF.

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

An FPGA implementation of modified decision based unsymmetrical trimmed median filter for the removal of salt and pepper noise in digital images

## Fig 2. Comparison graph of PSNR and IEF at different noise densities for Lena image.

### TABLE III COMPARISON OF PSNR VALUES OF DIFFERENT TEST IMAGES AT NOISE DENSITY OF 70%

| Test images | PSNR in dB |       |       |       |       |         |

|-------------|------------|-------|-------|-------|-------|---------|

|             | MF         | AMF   | PSMF  | DBA   | MDBA  | MDBUTMF |

| Cameraman   | 9.46       | 13.93 | 9.47  | 20.84 | 19.97 | 22.52   |

| Lena        | 9.93       | 15.25 | 9.84  | 22.64 | 22.47 | 24.30   |

| Baboon      | 10.11      | 14.86 | 10.05 | 22.35 | 20.54 | 23.80   |

The proposed algorithm is tested against images namely Cameraman, Baboon and Lena. The images are corrupted by 70% "Salt and Pepper" noise. The PSNR values of these images using different algorithms are given in Table III. From the table, it is clear that the MDBUTMF gives better PSNR values irrespective of the nature of the input image.

The MDBUTMF is also used to process the color images that are corrupted by salt and pepper noise. The color image taken into account is Baboon. In Fig. 4, the first column represents the processed image using MF at 80% and 90% noise densities. it can be observed that the performance of the proposed algorithm is better than the existing algorithms at high noise densities. Not all the elements in a selected 3 x 3 window is 255s or zeros at medium noise density. Hence, the proposed algorithm is almost same PSNR value against MDBUTMF at medium noise density. Subsequent columns represent the processed images for PSMF, DBA, MDBA and MDBUTMF. From the figure, it is possible to observe that the quality of the restored image using proposed algorithm is better than the quality of the restored image using existing algorithms.

Fig. 3. Results of different algorithms for Baboon image. (a) Output of MF. (b) Output of AMF. (c) Output of PSMF. (d) Output of DBA. (e) Output of MDBA.(f) Output of MDBUTMF. Row 1 and Row 2 show

International Conference on Electrical and Electronics Engineering (ICEEE 2012)-7th Oct, 2012, Bangalore- ISBN: 978-93-82208-25-9

processed results of various algorithms for image corrupted by 80% and 90% noise densities, respectively.

Fig. 4. Results of different algorithms for color Baboon image. (a) Output of MF. (b) Output of AMF. (c) Output of PSMF. (d) Output of DBA. (e) Output of MDBA. (f) Output of MDBUTMF. Rows 1 and 2 show processed results of various algorithms for color image corrupted by 70% and 80% noise densities, respectively.

### VI. CONCLUSION

A new algorithm (MDBUTMF) is proposed which gives better performance in comparison with the existing non-linear filter like Standard Median Filter (SMF), Adaptive Median Filter (AMF), Decision Based Algorithm (DBA) Modified Decision Based (MDBA), Algorithm and Progressive Switched Median Filter (PSMF) algorithms. These existing impulse noise removal algorithms are in terms of PSNR and IEF. The performance of the algorithm has been tested at low, medium and high noise densities on both gray-scale and color images. Even at high noise density levels the MDBUTMF gives better results .Both visual and quantitative results are demonstrated and it is also applied to many real-time

applications The proposed algorithm is effective for salt and pepper noise removal in images at high noise densities.

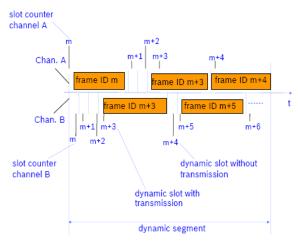

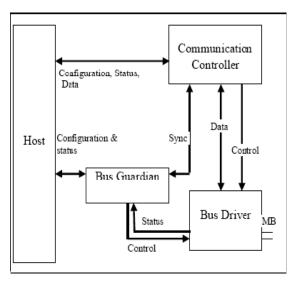

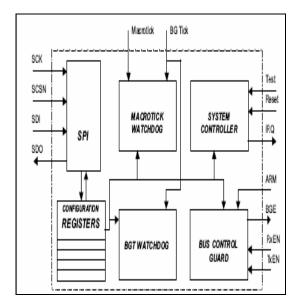

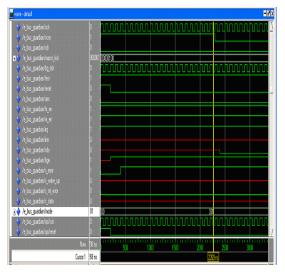

### REFERENCES