# Interscience Research Network Interscience Research Network

**Conference Proceedings - Full Volumes**

**IRNet Conference Proceedings**

Fall 9-16-2012

## Proceeding of International Conference on Future Trend in Electrical, Electronics and Computer Science Engineering

Prof. (Dr.) Srikanta Patnaik

Follow this and additional works at: https://www.interscience.in/conf\_proc\_volumes

Part of the Computational Engineering Commons, Computer Engineering Commons, and the Electrical and Computer Engineering Commons

### Editorial

Education has now become the instrument fashioned by men to achieve life's goals. As, it is being well observed by The Great Rabindra Nath Tagore "He who sees all being in his own self and his own self in all beings, he does not remain unrevealed", that should be the motto of our Indian educational Institutions. Science had become the twilight in this dark era without science life will become hell . The conference is a thought provoking outcome of all these interrelated facts.

Electrical, Electronics and Computer Science is the scientific and mathematical approach to computation, and specifically to the design of computing machines and processes. Its subfields can be divided into practical techniques for its implementation and application in computer systems and purely theoretical areas. Some, such as computational complexity theory, which studies fundamental properties of computational problems, are highly abstract, while others, such as computer graphics, emphasize real-world applications. Still others focus on the challenges in implementing computations. Modern society has seen a significant shift for Electrical, Electronics and Computer Science which is being used solely by experts or professionals to a more widespread user base.

The idea of the conference is for the scientists, scholars, engineers and students from the Universities all around the world and the industry to present ongoing research activities, and hence to foster research relations between the Universities and the Industry. This conference provides opportunities for the delegates to exchange new ideas and application experiences face to face, to establish business or research relations and to find global partners for future collaboration. Through this conference IRNet provides a forum for Research and Development.Moreover, it encourages academicians and researchers from all types of institutions and organizations. It aims to provide the platform for all to interact and share the domain knowledge with each other. Its motto to bring together developers, users, academicians and researchers for sharing and exploring new areas of research and development.

Prof. (Dr.) Srikanta Patnaik

Chairman, I.I.M.T., Bhubaneswar Intersceince Campus, At/Po.: Kantabada, Via-Janla, Dist-Khurda Bhubaneswar, Pin:752054. Orissa, INDIA

### MICROCONTROLLER BASED E – AGRICULTURE SYSTEM WITH VIDEO MONITORING

### <sup>1</sup>UMESH D DIXIT & <sup>2</sup>MALLANAGOUD N PATIL

<sup>1&2</sup> Department of Electronics & Communication Engineering, BLDEA's CET, Bijapur, India-586103

**Abstract:** E-Agriculture is a modern scientific technique in which electronic instruments can be used to control the various activities performed in the field. The agricultural works such as pumping the water to the farm, checking the moisture content of soil, fencing for the field, voltage regulation, applying the pesticides to the yield etc. can be easily performed by help of E-Agriculture system. The video monitoring helps real time remote monitoring of the field for pest identification by the experts and surveillance of the field by the owner.

Key Words: Microcontroller, Soil moisture sensor, Temperature sensor, Water level sensor, Pump lift sensor, Stepper Motor, Web camera, Transmitter, Receiver.

### **1.0 INTRODUCTION**

Modern agriculture activities require automation techniques from which farmer can perform his work to have high yield with low cost by taking the help of technology available. E-Agriculture system is a modern scientific technique in which electronic instruments can be used to control the various activities performed in the field. The agricultural works such as pumping the water to the farm, checking the moisture content of soil, fencing of the field, voltage regulation, applying of the pesticides to the yield with video monitoring can be easily performed by help of E-Agriculture system.

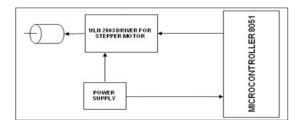

Here we propose a microcontroller based system that facilitates the farmer to adopt E-agriculture. The moisture sensors inserted in the ground absorbs the level of moisture, the microcontroller collects this information and then triggers the water pump to irrigate the field if the moisture level is less than the threshold value. The threshold value can be chosen based on the crops. The microcontroller also monitors water source. If the water level is below the normal condition, the pump is immediately switched off. The ultrasonic frequency generator is used for protecting the yields from the pests. The arrival of the animals can be avoided by using the electrical fencing system. This system delivers a mild shock to the animals when they try to enter into the field. The shock is not harmful to the animals, thus they move apart from the field. The pump is protected from the thief by using the pump lift sensor (transmitter and receiver).

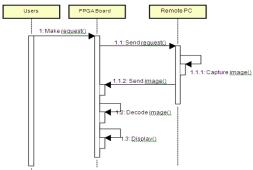

The wireless web camera installed in the field helps real time monitoring of the field to identify pests, growth of the plant by the experts to seek required suggestions. The video monitoring could also help the owner to identify the work going on the field.

### 2.0 METHODOLOGY

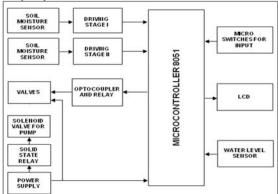

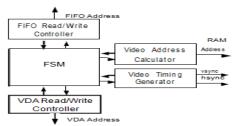

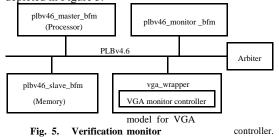

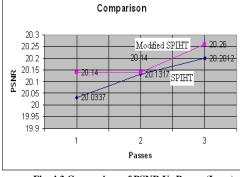

The Figure 1 shows the proposed model for E-Agriculture The system consists of soil moisture sensors, temperature sensors, water level sensor, pump lift sensor, piezo sensor, electrical fencing system, transmitter and receiver controlled by an 8-bit microcontroller. The soil moisture sensors are used to absorb the level of the moisture. This information is used by the microcontroller to switch ON or OFF the water pump. If the moisture level is less than the specified Min. value, the pump is switched ON and if the value exceeds the specified maximum value, the pump is switched OFF automatically. The Min and Max values for moisture level can be chosen depending on the crops.

The temperature sensor is used to detect overheating of pump due to variation in supply voltage. Water level sensor is used to detect the water level conditions and causes microcontroller to take appropriate action if the water level is below the specified limit. The pump lift sensor helps to prevent the pump from thieves.

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

Figure 1. System arrangements in the Field

Figure 2. System arrangements at user side

The piezo crystal is used for ultrasonic frequency generation to protect the yields from the pests. The arrival of the animals can be avoided by using the electrical fencing system. This system delivers a mild shock to the animals when they try to enter into the field. The shock is not harmful to the animals, thus they move apart from the field. The transmitter in the system is used to send information, if an attempt is made to steal the pump.

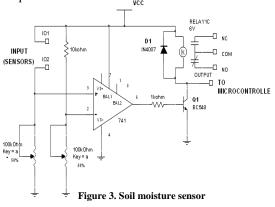

### 2.1 SOIL MOISTURE SENSOR

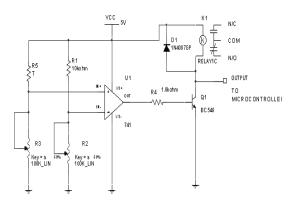

Figure 3 shows the circuit diagram of Soil Sensing. It consists of Soil Sensor (Copper Conducting Plates), OPAMP, Transistor and Relay. The resistance offered by the sensor depends on moisture level. It is inversely proportional to the moisture condition. The OPAMP is used as a voltage comparator. The increase in moisture content causes change in voltage at comparator input and the output of the comparator goes from its low to high state. The output of the comparator turns the transistor ON, which drives the relay. The relay can be used to switch ON/OFF the water pump depending on requirements.

#### 2.2 TEMPERATURE SENSOR

Figure 4. Temperature sensor

The temperature sensing circuit is designed with thermistor, OPAMP, Transistor and Relay as shown in Figure 4. Here the OPAMP is used as a voltage comparator. The thermistor 'T' and variable resistor VR1 are connected to the non-inverting terminal to provide the potential difference. The inverting terminal gets the potential difference from resistor R1 and variable resistor VR2, to adjust the reference voltage. The thermistor resistance will be high under normal temperature. So the voltage at non-inverting terminal is less than the reference voltage. As soon as temperature increases, the thermistor resistance decreases which causes an increase in the voltage at non-inverting terminal of the OP\_AMP. Because of this condition the potential difference between two inputs of comparator changes and the output of the comparator goes from its low to high state and turns the transistor ON. The relay connected to the transistor in turn switch OFF the water pump. Thus it protects the pump from overheating.

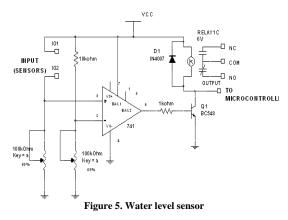

### 2.3 WATER LEVEL SENSOR

The Figure 5 show the arrangements used for water level sensor. It works similar to the above two sensors discussed in the section 2.1 and 2.2. Depending on the water level, the relay turns the water pump ON/OFF as required.

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

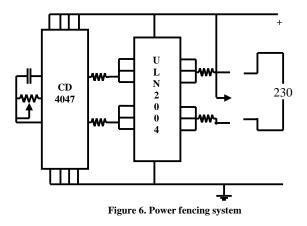

### 2.4 POWER FENCING SYSTEM

The Figure 6 shows the circuit arrangement for power fencing system. It is designed with CD 4047 astable/monostable multivibrator and ULN 2003, a darlington pair array (current amplification) ICs. Here CD4047 is used astable multivibrator which generates a frequency of 8 KHz. The wave shape of such circuit is a quasi sine wave. The amplitude of this signal is not enough to drive a transformer for step-up application. Therefore ULN 2003 a 7 channel is used to drive the step up transformer. The respective outputs of particular channel are connected to a stepup transformer and the output is taken across secondary of the transformer which is a high voltage AC. The voltage developed across output is connected to fencing arrangements. The output of this circuit is not injurious but leads to a mild shock.

### 2.5 ULTRASONIC PEST REPELLER

Pests like rats, rodents, rabbits, birds, get irritated by ultrasonic frequency in the range of 30 to 50KHz. Fortunately these frequencies are inaudible to humans. These frequencies can be used to get rid of the pests. But all these pests do not react to the same ultrasonic frequency. Some pests may get repelled at 38 to 48 KHz while some others may react at 35 KHz. To increase the effectiveness we used a continuously varying ultrasonic frequency oscillator. The circuit is designed using 555 timer, CD4017 a decade counter with some presets.

### 2.6 VIDEO MONITORING

Figure 7. Video monitoring system

The video monitoring helps to observe the field operations from a remote place. It can also be used by the experts to seek any required suggestions from a remote place. Such as agriculture officer can view the things from a remote place and provide necessary suggestions. Here we used surveillance camera for video monitoring. Surveillance cameras are closedcircuit television (CCTV) cameras that transmit a video and audio signal to a wireless receiver through a radio band. The Figure 7 shows the camera used with it's arrangements. The camera used supports a transmission range of about 500 feets with high quality video. It also supports multiple receivers to receive the video signal.

### 3.0 IMPLEMETATION

The system is implemented using ATMEL89C52 microcontroller. The table 1 gives details about sensor and water pump connections with ports of 89C52 and table 2 gives details about different conditions of sensors and water pump.

Table 1. Sensor and Water pump connections

| 14010  | 1. Sensor and water pump | e o mile e momo  |

|--------|--------------------------|------------------|

| Sl.No. | Connections              | Port Pins        |

| 01.    | Soil moisture sensor     | P1.0             |

| 02.    | Water level sensor       | P1.1             |

| 03.    | Temperature sensor       | P1.2             |

| 04     | Power supply to pump     | P2.0             |

| T-1-1- | 2 C                      | De ut et et et e |

Table 2. Sensor, Water pump and Port status

| Sl. | Sensor and Pump      | Pin Status |

|-----|----------------------|------------|

| No. | Condition            |            |

| 01  | Soil is DRY          | P1.0(HIGH) |

| 02  | Soil is WET          | P1.0(LOW)  |

| 03  | Water is PRESENT     | P1.1(HIGH) |

| 04  | Water is ABSENT      | P1.1(LOW)  |

| 05  | Temperature NORMAL   | P1.2(LOW)  |

| 06  | Temperature ABNORMAL | P1.2(HIGH) |

| 07  | Water pump ON        | P2.0(HIGH) |

| 08  | Water pump OFF       | P2.1(LOW)  |

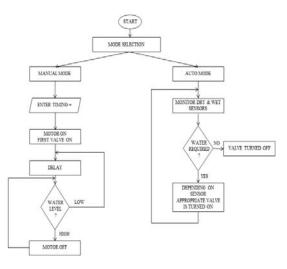

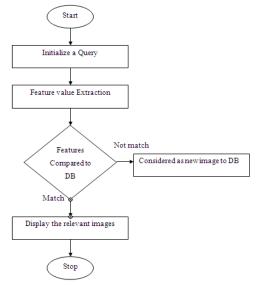

**Figure 8 Flow chart**

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

The Figure 8 shows the flow chart for e-agriculture system. The system reads the data from moisture level sensor, water level sensor and temperature sensor connected to water pump. The pump lift sensor, ultrasonic repeller and power fencing system work independently i.e they are not controlled by the microcontroller. The pump lift sensor generates an alarm sound at transmitter, if an attempt is made to steal the pump, so that the farmer can take necessary action. When the system is switched ON, the program tests whether the soil is dry. If the soil is dry, the program then tests the availability of the water source. If water level is sufficient, and temperature of the pump is normal, the water pump is turned ON. Once the pump is turned ON, the system again tests water level, temperature and moisture level continuously. If the water level is insufficient or if the pump is overheated or if the soil moisture level is sufficient, the water pump is switched OFF.

### 4.0 RESULTS AND DISCUSSION

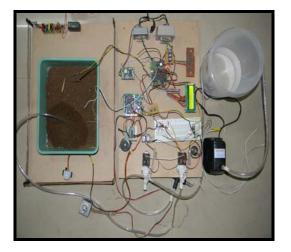

The Figure 9 shows the model of proposed eagriculture with video monitoring system. The model is built and tested. All the required conditions are tested and thus the results of the system found satisfactory. As the system supplies the water depending on the crops requirement, the system saves water source and also power consumed by the water pump. We are trying to implement the same in the field and hoping the best results from the system..

Figure 9. Model with all arrangements

### 5.0 CONCLUSION AND FUTURE SCOPE

The E-Agriculture system provides the best results and helps the farmers to control agriculture operations. The video monitoring could be used by the experts to provide suggestions from a remote place. Even though the initial installing cost is little more, the life period of the system is long.

#### 6.0 REFERENCES

- Microcontroller based E-agriculture system-M N Patil, U D Dixit, A S Jadhav – ICEICE-2010.

- [2] The 8051 Microcontroller, 3rd Edition Kenneth J. Ayala

- [3] The 8051 Microcontroller and Embedded Systems Mohd. Ali Mazidi, Janice Gillispie Mazidi.

- [4] Op-amps and Linear integrated circuits Ramakant Gayakwad

- [5] Scheduling Automatic Irrigation by threshold-set soil matric Potential Increases Irrigation Efficiency while Minimzing Plant Stress – Isaac Klein.

- [6] Description of an autonomous automatic photo voltaic irrigation system – Voudoubas John.

- [7] http://en.wikipedia.org/wiki/E-agriculture

- [8] http://www.scribd.com

- [9] http://www.e-agriculture.org/about.html

- [10] http://www.odi.org.uk/resources/download/164.pdf

- [11] http://www.itu.int/wsis/docs/geneva/official/poa.html

- [12] http://www.itu.int/wsis/docs2/tunis/off/6rev1.html

**~~**

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

### TREE BASED IMAGE COMPRESSION TECHNIQUE

### <sup>1</sup>RASHMI HANCHINAL & <sup>2</sup>SAVITRI RAJU

<sup>1</sup>BLDEA's Dr. P. G. Halakatti College of Engineering and Technology Bijapur -586103, Karnataka, India <sup>2</sup>SDM, College of Engineering and Technology, Dhavalagiri, Dharwad-580002, Karnataka, India.

**Abstract**—The objective of this paper is to present one of the tree based image compression technique, i.e. Set Partitioning In Hierarchical Trees (SPIHT), is considered for encoding and decoding image data. The proposed method decomposes an image into several subband images using the discrete wavelet transform, decor related coefficients quantized by SPIHT algorithm. In this paper, biorthogonal wavelet has been used to perform the transform of a test image and their results have been discussed. Simulation results obtained using MATLAB shows that the output image has better Peak Signal to Noise Ratio (PSNR).

**Keywords**— Peak Signal to Noise Ratio (PSNR), Discrete Wavelet Transform (DWT), Mean Squared Error (MSE), Set Partitioning In Hierarchical Trees (SPIHT), MATLAB.

### I. INTRODUCTION

The fundamental goal of image compression is to reduce the bit rate for transmission or storage while maintaining an acceptable fidelity or image quality. Image compression can be lossy or lossless. The lossless compression techniques are reversible or non destructive compression. It is guaranteed that the decompression image is identical to the original image, whereas in lossy compression technique the reconstructed image is not identical to the original image.

Various types of coding techniques were proposed for the Image processing Application. The two techniques used are: Predictive coding and Transform coding.

Predictive coding is a technique where information already sent or available is used to predict future values, and the difference is coded. Since this is done in the image or spatial domain, it is relatively simple to implement and is readily adapted to local image characteristics. Differential Pulse Code Modulation (DPCM) is one particular example of predictive coding.

Transform coding, on the other hand, first transforms the image from its spatial domain representation to a different type of representation using some well-known transform and then codes the transformed coefficient values. This method provides greater data compression compared to predictive methods, although at the expense of greater computation.

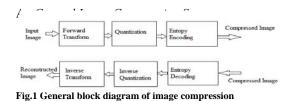

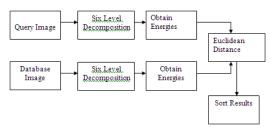

The general block diagram of the image compression system is shown in figure 1.It consists of three main components viz; 1) Transform 2) Quantization 3) Entropy Encoding.Compression is achieved by applying a wavelet transforms in order to decorrelate the image data, quantizing the resulting transform coefficients and entropy coding the quantized values. First, the image is transformed into a domain where the image information is represented in a more compact form; here we have used discrete wavelet transform. Quantization refers to the process of approximating the continuous set of values in the image data with a finite, preferably small, set of values. The input to a quantizer is the original data and the output is always one among a finite number of levels. The quantizer is a function whose set of output values are discrete and usually finite. Obviously, this is a process of approximation and a good quantizer is one which represents the original signal with minimum loss or distortion. A quantizer is used to reduce the number of bits needed to store the transformed coefficients.

Entropy coding is used to compress sequence of quantized wavelet coefficients from quantization step further increase compression, without loss. Entropy coder is optional; it is used only when a little more compression is desired.

### **II. WAVELET TRANSFORM**

Wavelet Transform has emerged as a powerful mathematical tool in many areas of science and engineering specifically for data compression. It has provided a promising vehicle for image processing applications, because of its flexibility in representing images and its ability to take into account Human Visual System characteristic. It is mainly used to decorrelate the image data, so the resulting coefficients can be efficiently coded. It also has good

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

energy compaction capabilities, which results in a high compression ratio.

Wavelets are functions generated from one single function (basis function) called the prototype or mother wavelet by dilations (scaling) and translations (shifts) in time (frequency) domain.

If the mother wavelet is denoted by  $\psi(t)$ , the other wavelets  $\psi_{a,b}(t)$  can be represented as

(1)

where a and b are two arbitrary real numbers. The variables a and b represent the parameters for dilations and translations respectively in the time axis.

The translation parameter b relates to the location of the wavelet function as it is shifted through the signal. Thus, it corresponds to the time information in the Wavelet Transform. The scale parameter a is defined as |1/frequency| and corresponds to frequency information. Scaling either dilates (expands) or compresses a signal. Large scales (low frequencies) dilate the signal and provide detailed information hidden in the signal, while small scales (high frequencies) compress the signal and provide global information about the signal.

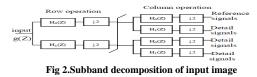

Based on this definition of wavelets, the wavelet transform (WT) of a function (signal) f (t) is mathematically represented by

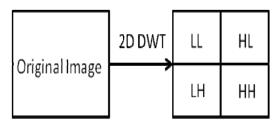

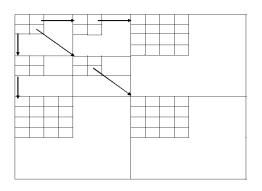

The Wavelet Transform, at high frequencies, gives good time resolution and poor frequency resolution, while at low frequencies; the Wavelet Transform gives good frequency resolution and poor time resolution. The Discrete Wavelet Transform decomposes the image into two subbands by passing it through a low pass filter (LP) and a high pass filter (HP) and sub sampling the output of the two filters by two. At each level, the high pass filter produces detail information, while the low pass filter associated with scaling function produces coarse approximations as shown in fig.2 [3]The filtering increases the frequency resolution by 2 and the sub sampling reduces the time resolution by 2. This process is iterated on the low pass branch to obtain finer frequency resolution at lower frequencies. The output subsequences of the low pass branch corresponding to the last iteration and the output subsequence of all the high pass branches in this iterative scheme are collected as the DWT coefficients at various resolutions.

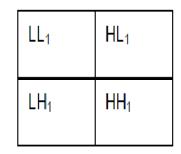

Fig. 3 Subbands of single level 2 dimensional

Four subbands arise when wavelet transform is applied in two dimensions (vertical and horizontal) as shown in fig. 3. The subbands labelled LH1, HL1 and HH1 represent the finest scale wavelet coefficients. At each coarser level, the coefficients represent a larger spatial area of the image, but a narrower band of frequencies.

### **III.SPIHT**

(2)

SPIHT is primarily a wavelet-based image compression scheme. SPIHT stands for Set Partitioning in Hierarchical Trees. The SPIHT algorithm, developed by Said and Pearlman in 1996 [1], is a fast and efficient image compression algorithm that works by testing ordered wavelet coefficients for significance in a decreasing bit plane order, and quantizing only the significant coefficients. The high coding efficiency obtained by this algorithm is due to a group testing of the coefficients that belong to a wavelet tree. Group testing is advantageous because of the inter-band correlation that exists between the coefficients belonging to a tree. The SPIHT uses the fundamental idea of zero-tree coding from the EZW [2] but is able to obtain a more efficient and better compression performance in most cases without having to use an arithmetic encoder. The zerotree is based on the hypothesis that if a wavelet coefficient at a coarser level is insignificant with respect to a given threshold, then all wavelet coefficients of the same orientation in the same spatial location at finer scales are likely to be insignificant with respect to the same threshold. For still image compression, SPIHT achieves considerably better quality when compared JPEG [7],

The SPIHT coding operates by exploiting the relationships among the wavelet coefficients across the different scales at the same spatial location in the wavelet subbands. In general, SPIHT coding involves the coding of the position of significant wavelet coefficients and the coding of the position of zerotrees in the wavelet subbands. The SPIHT coder exploits the following image characteristics: 1) The majority of an image's energy is concentrated in the low frequency components and a decrease in variance is observed as we move from the highest to the lowest levels of the subband pyramid and 2) It has been

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

observed that there is a spatial self-similarity among the subbands, and the coefficients are likely to be better magnitude-ordered if we move downward in the pyramid along the same spatial orientation. Each subband is quantized differently depending on its importance, which is often on its energy content or variance [8].

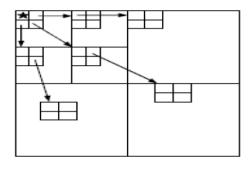

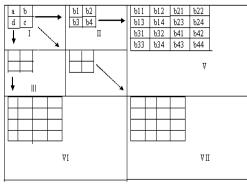

Fig.4 Spatial orientation tree defined in a pyramid constructed with recursive four-subband splitting

A tree structure, called spatial orientation tree, naturally defines the spatial relationship on the hierarchical pyramid [4]. Fig. 4 shows how the spatial orientation tree is defined in a pyramid constructed with recursive four-subband splitting. Every pixel in the image signifies a node in the tree and is determined by its corresponding pixel coordinate. Its direct descendants (offspring) symbolize the pixels of the same spatial orientation in the next finer level of the pyramid. The tree is defined in such a way that each node has either no offspring or four off-springs, which always form a group of 2X2 adjacent pixels. The pixels in the highest level of the pyramid are the tree roots and are also grouped in 2X2 adjacent pixels. However, their offspring branching is different, and in each group one of them has no descendants.

### **IV.CODING ALGORITHM**

The algorithm starts at the coarsest sub band in the sub band pyramid. SPIHT captures the current bit-plane information of all the DWT coefficients and organizes them into three subsets: (1) List of Significant Pixels (LSP), (2) List of Insignificant Pixels (LIP) and (3) List of Insignificant Sets of Pixels (LIS). LSP constitutes the coordinates of all coefficients that are significant. LIS contains the roots of insignificant sets of coefficient. Finally, LIP contains a list of all coefficients that do not belong to either LIS or LSP and are insignificant.

The following are the sets of coordinates used to represent the coding method:

- O(i, j) : set of coordinates of all offspring of node (i, j)

- D(i,j): set of coordinates of all descendants of the node (i,j)

- *H*(*i*, *j*) : set of coordinates of all spatial orientation tree roots (nodes in the highest pyramid level).

- L(i,j) = D(i,j) O(i,j). This set contains all the descendants of tree node (i,j), except its four offspring.

Except for the highest and lowest pyramid levels, the set partitioning trees has,

$O(i,j) = \{(2i,2j); (2i,2j+1); (2i+1,2j); (2i+1,2j+1)\}$

The set partitioning rules are simply the following:

- 1) The initial partition is formed with the sets (i, j) and D(i, j), for all  $(i, j) \in H$ .

- 2) If D(i, j) is significant, then it is partitioned into L(i, j) plus the four single-element sets with  $(k, l) \in O(i, j)$ . In other words if any of the descendants of node (i, j) is significant ,then its four offspring becomes four new sets and all its other descendants become another set(to be tested in next step)

- 3) If L(i,j) is significant, then it is partitioned into the four sets D(k,l), with  $(k,l) \in O(i,j)$ .

The significance function is defined as follows:

$$s_n(\tau) = \begin{cases} 1, & \max_{(i,j)\in\tau}\{|c_{i,j}|\} \ge 2^n, \\ 0, & otherwise \end{cases}$$

(3)

A. Algorithm

The algorithm consists of following steps:

- 1. Initialization

- 2. Sorting Pass

- 3. Refinement Pass

- 4. Quantization-step update

**1) Initialization:** Output  $n = \lfloor \log_2 \binom{max}{(i,j)} \{ |c_{(i,j)}| \} \rfloor$  set the LSP as an empty list, and add the coordinates  $(i, j) \in H$  to the LIP, and only those with descendants also to the LIS, as type *A* entries.

### 2) Sorting Pass:

2.1) For each entry (i, j) in the LIP do:

2.1.1) Output  $s_n(i, j)$ ;

2.1.2) If  $s_n(i,j) = 1$  then move (i,j) to the LSP and output the sign of  $C_{(i,j)}$ ;

2.2) For each entry (i, j) in the LIS do:

2.2.1) If the entry is of type A then

• Output

$$s_n(D(i,j))$$

;

• If

$$s_n(D(i,j)) = 1$$

then

\* For each

$$(k, l) \in (i, j)$$

do:

• Output

$$s_n(k, l)$$

;

- If  $s_n(k, l) = 1$  then add (k, l) to the LSP and output the sign of  $C_{(i,j)}$

- If  $s_n(k, l) = 0$  then add (k, l) to the LIP

\* If L  $(i, j) # \emptyset$  then move (i, j) to the end of the LIS, as an entry of type *B*, and go to

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

Step 2.2.2); otherwise, remove entry from the LIS; 2.2.2) If the entry is of type *B* then • Output ; • If = 1 then \* Add each to the end of the LIS as an entry of type A; \* Remove from the LIS.

3) **Refinement Pass:** For each entry in the LSP, except those included in the last sorting pass (i.e., with same n), output the  $n^{th}$  most significant bit of |;

4) Quantization-Step Update: Decrement *n* by 1 and go to Step 2.

V. IMAGE QUALITY MEASUREMENT

Mean Squared Error (MSE) and Peak Signal noise ratio (PSNR) are the most common methods for measuring the quality of compressed image. Mean Square Error is given by:

Peak Signal to Noise Ratio is given as:

$PSNR = 10log_{10} (255)^2 / MSE$

### VI.SIMULATION RESULTS

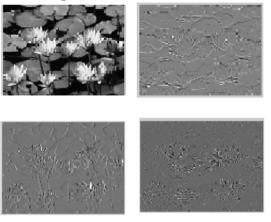

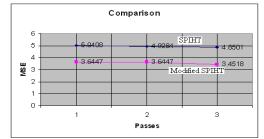

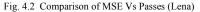

SPIHT Encoding/Decoding has been implemented in MATLAB 7.10 and tested on the different images of size 256×256. Biorthogonal wavelet filters are used and DWT level is kept to 8 and bit rate=1.The simulation results obtained are tabulated in table 1.

| Wavelet       |      | Bior3.5 | Bior4.4 | Bior5<br>.5 | Bior<br>6.8 |

|---------------|------|---------|---------|-------------|-------------|

| Knee<br>Image | MSE  | 20.49   | 15.91   | 18.63       | 15.5<br>1   |

| mage          | PSNR | 35.01   | 36.09   | 35.42       | 36.2<br>2   |

| Zelda         | MSE  | 11.66   | 8.81    | 9.99        | 8.77        |

| Image         | PSNR | 37.46   | 38.68   | 38.13       | 38.6<br>9   |

| Satellite     | MSE  | 29.72   | 6.32    | 8.18        | 6.57        |

| Image         | PSNR | 33.39   | 40.12   | 38.99       | 39.9<br>5   |

TABLE I SIMULATION RESULTS

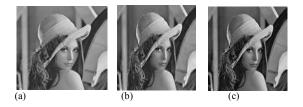

Fig.5 shows the original Zelda image, Fig.6 shows Decomposed image at level 8 and Fig.7 shows the reconstructed Zelda image.

Fig.5 Original Zelda Image

Fig.6 Decomposed image at level 8

Fig.7 Reconstructed Zelda Image

### VII. CONCLUSION

This paper has presented the wavelet based image compression technique .The algorithm is tested on different images of size 256×256 .The simulation results shows good image quality and high PSNR for gray scale images. Further the algorithm can be tested on the colour images of different size.

### REFERENCES

- A.Said, and W.A.Pearlman, A New, Fast and Efficient Image Codec Based on Set Partitioning in Hierarchical Trees IEEE transactions on circuits and systems for Video Tech, vol.6, no.3, pp.243-250, June 1996.

- [2] J.M. Shapiro, "Embedded image coding using the zero trees of wavelet coefficients", IEEE Transactions on Image Processing, Vol. 41, No. 12, pp. 3445-3462, December 1993

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

- [3] K. Sayood, "Introduction to Data Compression", 2<sup>nd</sup> Ed., Academic Press, Morgan Kaufmann Publishers, 2000.

- [4] R.Sudhakar and Ms R Karthiga and S.Jayaraman Image Compression using Coding of Wavelet Coefficients – A Survey, GVIP Special Issue on Image Compression, 2007.

- [5] K.P.Soman & K.I.Ramachandran "Insight into Wavelets from theory to practice", Prentice Hall India, New Delhi, 2009.

- [6] David Salomon, "Data compression", the complete reference, 3<sup>rd</sup> Ed. Springer-Verlag New York, Inc. 2005, page no.597-605.

- [7] Savitri Raju and Mriyunjaya V Latte, "Comparision of compression algorithms", Proceeding of two- day national conference on , convergence of signal processing , communication and VLSI Design, page no.85-87.

- [8] Raghuveer Rao and Ajit Bopardikar, "Wavelet Transform-Introduction to Theory and Applications", Addison Wesley Pearson Edu. Edition, 2002.

$\otimes \otimes \otimes$

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

### HIGH SPEED UNIFIED BINARY AND BCD DDITION/SUBTRACTION UNIT WITH A NOVEL CORRECTION FREE APPROACH

<sup>1</sup>A. SRINIVAS & <sup>2</sup>SRIVANI. V

<sup>1,2</sup>Kakatiya Institute of Technology & Science, Warangal, India

**Abstract**— Scientific, internet- based, financial applications require processing of decimal data with high precision. This paper proposes a novel correction-free decimal adder which has reduced delay. This 1-digit adder BCD adder is used to build 8-digit decimal adder with a carry look ahead like approach. This 8-digit BCD adder is then used to create a combined binary and decimal addition, subtraction unit. Reduced area and high performance carry select adder is designed for binary unit. This 32-bit binary and BCD addition, subtraction unit is mapped on Xilinx Virtex-4 FPGA and synthesized using ISE 13.4i Xilinx design tools.

Keywords-BCD; correction; synthesis; VerilogHDL

### I. INTRODUCTION

In this era of electronics computing based financial, internet, commercial and industrial control applications, high precision arithmetic operations on decimal operands is required. Binary arithmetic is used in most of the computing applications but binary approximation creates incorrect results. Therefore, Binary Decimal Arithmetic is the solution. Performing decimal operations over binary-based hardware requires the conversion of decimal operands to binary and then conversion of results to decimal. These conversions degrade the performance of the system. Software solutions are 100 to 1000 times slower than hardware counterparts, so these are not preferable. Therefore, there is growing importance of decimal arithmetic in hardware.

To facilitate binary applications on the same hardware a reconfigurable approach is to be adopted. This paper deals with flexible hardware solutions for both decimal and binary processing. The proposed design can perform both binary and BCD addition/subtraction.

We develop a high speed BCD digit adder with only two stages in contrary to traditional BCD digit adder which requires three stages (binary addition, carry calculation, correction). First stage inputs are the three most significant bits of each operand. Second stage inputs are the output of first stage, least significant bits of each operand and the input carry (total of seven bits). Hence, our design eliminates correction stage.

We then use our high speed digit BCD adder to develop an 8-digit BCD adder which uses precomputed carries. This 8-digit adder and 32-bit binary adder are combined to form unified binary and BCD addition/subtraction unit.

All the existing architectures, as per the knowledge of the authors, use 10's or 9's complementers to

implement subtraction in BCD. This has high latency. Therefore, a new approach has been proposed to overcome this problem.

Implementation results show that our proposed design exhibits better speed while preserving an area advantage over most of the existing units.

The remainder of this paper is organized as follows: Section II presents a brief background of BCD arithmetic and related work. Section III exhibits the details of optimized correction-free BCD digit adder. Section IV discusses about the proposed 8digit decimal adder. Section V deals with the proposed binary adder. Section VI presents our unified binary and BCD addition/subtraction unit. In Section VII, synthesis report and comparison results are presented and section VIII concludes the paper.

### II. BACKGROUND FOR BCD ARITHMETIC

Binary Coded Decimal (BCD) is used for expressing decimal digits with binary code. Decimal digits from 0 to 9 are represented using first 4-bit binary code groups  $(0000_2 \text{ to } 1001_2)$ . Remaining 4-bit binary code groups  $1010_2 \text{ to } 1111_2$  for decimal digits 10 to 15 are not used when BCD arithmetic is considered. Hence addition of two BCD digits produces incorrect results if sum exceeds largest BCD digit 9(1001\_2). In those cases, the sum result is corrected by adding 6(0110\_2). The decimal carry result generated by this process is added to the next higher two BCD digits in the BCD operands to be added.

Generally, subtraction is performed by adding A to the 10's complement of B, where A and B are operands used for subtraction. But, 10's complement can also be obtained by adding 1 to the 9's complement of that number. 9's complement can also be computed by adding  $1010_2$  to the one's complement of a digit and taking the four least significant bits of the result. One's complement is

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

computed by inverting bits of that digit. This approach is used in this paper in the design of unified binary and BCD addition/subtraction unit.

## III. OPTIMIZED CORRECTION-FREE BCD DIGIT ADDER

Traditional BCD digit adder requires three stages which includes the correction stage. This correction stage performs the correction by adding  $(0110)_2$  to the result when the first stage result is greater than 9 =  $(1001)_{BCD}$ . But, this correction stage degrades the performance of the decimal adder. Therefore, we propose a correction-free BCD digit adder in this section.

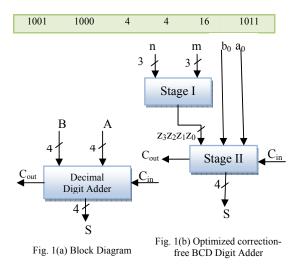

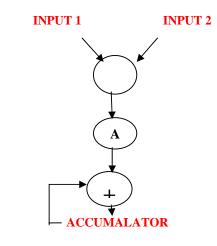

We consider two decimal input digits to the decimal adder shown in fig. 1(a) as A {0, 9} and B{0, 9}, and decimal carry input is C<sub>in</sub>. Assume that the decimal sum output is S {0, 9} and the decimal carry output is C<sub>out</sub>. 8421 BCD representation of A, B and S can be written as  $A=a_3a_2a_1a_0$ ,  $B=b_3b_2b_1b_0$  and  $S=s_3s_2s_1s_0$  where  $a_i$ ,  $b_i$  and  $s_i$  for all  $i = \{0, 1, 2, 3\}$ . A and B can be expressed in terms of two integers  $m=a_3a_2a_1$  and  $n=b_3b_2b_1$  as:  $A=2 \times m + a_0$  and  $B=2 \times n + b_0$ , where  $0 \le m \le 4$  and  $0 \le n \le 4$ . This implies that the output of the BCD adder can be expressed as:

$\{C_{out}, Sum\} = A + B + C_{in} = (2 \times m + a_0) + (2 \times n + b_0) + C_{in}$

We can rearrange the equation as

$\{C_{out}, Sum\} = 2 \times (n + m) + (a_0 + b_0 + C_{in}).$

Based on this formula we have designed the BCD digit adder such that it consists of two stages: Stage I and Stage II. Figure 1(b) shows the block diagram of the proposed BCD adder. The inputs to Stage I are m and n. Stage I generates partial decimal sum: Z =  $z_3z_2z_1z_00 = 2 \times (m+n)$ . It should be noticed that this partial decimal sum consists of an even decimal digit  $(z_2z_1z_00)$  and a decimal carry  $z_3$  that can be either 1 or 0 based on the values of m and n. For example, if the two input decimal digits A and B are  $7 = (0111)_{BCD}$ and  $8 = (1000)_{BCD}$ , respectively, then we have: m =  $(011)_2$  = 3 , n =  $(100)_2$  = 4 and Z =  $z_3 z_2 z_1 z_0 0$  = 2  $\times$  $(m+n) = 2 \times (3 + 4) = (14)_{10}$ . This means that the decimal carry z<sub>3</sub> is 1 and the even decimal digit  $z_2 z_1 z_0 0 = (4)_{10} = (0100)_{BCD}$ . Since the produced decimal digit is always even, only  $z_3z_2z_1z_0$  are forwarded to Stage II of the BCD digit adder. Three more examples are listed in Table I for clarity.

The outputs of Stage I along with  $a_0$ ,  $b_0$  and  $C_{in}$  are fed to Stage II. For the purpose of designing Stage II, the values of  $C_{out}$ ,  $s_3$ ,  $s_2$ ,  $s_1$  and  $s_0$  have been calculated for all possible combinations of  $z_3$ ,  $z_2$ ,  $z_1$ ,  $z_0$ ,  $a_0$ ,  $b_0$ , and  $C_{in}$ . To illustrate this procedure, three possible combinations are presented in Table II.

TABLE I. EXAMPLES THAT DEMONSTRATE HOW THE OUTPUT OF STAGE I IS COMPUTED

|                    | 001101             |                   | 0110 00 |                   | ,    |

|--------------------|--------------------|-------------------|---------|-------------------|------|

| (A) <sub>BCD</sub> | (B) <sub>BCD</sub> | (m) <sub>10</sub> |         | (Z) <sub>10</sub> |      |

| 0011               | 0110               | 1                 | 3       | 8                 | 0100 |

| 0100               | 1001               | 2                 | 4       | 12                | 1001 |

Fig. 1 BCD Digit Adders

For example, in the first row of the table the values of  $z_3$ ,  $z_2$ ,  $z_1$ , and  $z_0$  are 1, 0, 1, and 1, respectively. This means that the value of  $2 \times (m + n)$  that is to be added to the value of  $(a_0 + b_0 + C_{in})$  is  $(16)_{10}$ . Since  $a_0$ ,  $b_0$ , and  $C_{in}$  in the example are 1, 0, and 0, respectively, the value of  $A+B = 2 \times (n + m) + (a_0 + b_0 + C_{in})$  is  $(17)_{10}$ . Therefore, the computed values for  $C_{out}$ ,  $s_3$ ,  $s_2$ ,  $s_1$ , and  $s_0$  are 1, 0, 1, 1, and 1, respectively. Based on this, Stage II generates the decimal sum output and the decimal carry output. Decimal carry output equation obtained is given by

$$C_{out} = z_2 C_{in} b_0 + z_2 C_{in} a_0 + z_2 a_0 b_0 + z_3.$$

It can be emphasized that our design does not require any corrections to the results, and the results are computed with only two stages. As it will be shown in Section VII, this enables our design to achieve better performance over other designs.

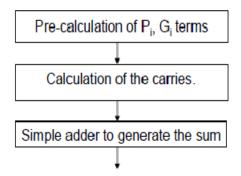

### IV. PROPOSED 8-DIGIT BCD ADDER

N single-BCD digit adders can be cascaded in a carry ripple fashion, in order to build N-digit BCD adder. Due to the dependency between the carries, long carry chain is introduced. But, carry rippling imposes large latency on the design. This carry chain can be observed in the logic equation of  $C_{out}$  (Section III).

TABLE II. EXAMPLES THAT DEMONSTRATE HOW THE OUTPUT OF STAGE II IS COMPUTED

| $\mathbf{Z}_3\mathbf{Z}_2\mathbf{Z}_1\mathbf{Z}_0$ | (Z) <sub>10</sub> | a <sub>0</sub> | b <sub>0</sub> | C <sub>in</sub> | C <sub>out</sub> | S <sub>3</sub> S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> |

|----------------------------------------------------|-------------------|----------------|----------------|-----------------|------------------|-------------------------------------------------------------|

| 1011                                               | 16                | 1              | 0              | 0               | 1                | 0111                                                        |

| 1001                                               | 12                | 0              | 1              | 0               | 1                | 0011                                                        |

| 0100                                               | 8                 | 1              | 0              | 1               | 1                | 0000                                                        |

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

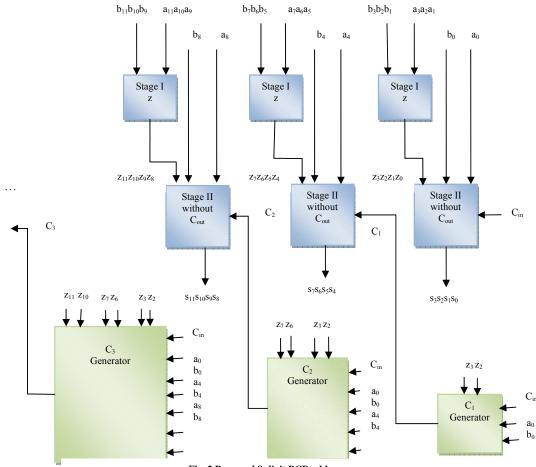

Fig. 2 Proposed 8-digit BCD adder

We assume that the general BCD representation for the  $i_{th}$  BCD digit is  $A_i = (a_{4j-1}a_{4j-2} a_{4j-3}a_{4j-4})_{BCD}$ where j = (i+1). For example,  $A_0 = (a_{3}a_2a_1a_0)_{BCD}$  while  $A_6 = (a_{27}a_{26}a_{25}a_{24})_{BCD}$ . Based on this assumption and referring to Figure 1(b),  $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ ,  $C_5$ ,  $C_6$ ,  $C_7$ , and  $C_8$  in an 8-digit carry ripple BCD adder are computed using the logic equation of  $C_{out}$  of Section III with some algebraic manipulation. In general we can write:

$$C_{i+1} = z_{4(i+1)} - 2(C_i(b_{4i} + a_{4i}) + a_{4i}b_{4i}) + z_{4(i+1)-1}.$$

It is clear from the previous equation that there is a dependency between the carries which will definitely affect the overall performance of the system. Therefore, in our proposed 8-digit BCD adder, we break down the carry chain by directly computing the carries from the inputs in a carry look ahead like approach. We modify Stage II of our BCD-digit adder such that it does not generate a carry anymore. The carry is instead generated using a carry generation block which is a direct function of the inputs (the output of Stage I and the operands as shown in Figure 2 which presents the first three stages of the proposed 8-digit BCD adder). The carry signal is

found by substituting the equations of all previous carries into the equation of that carry signal. For example,  $C_2$  is calculated using  $a_0$ ,  $b_0$ ,  $a_4$ ,  $b_4$ ,  $z_2$ ,  $z_3$ ,  $z_6$ ,  $z_7$ , and  $C_{in}$ . By adopting this approach we could break the carry chain and achieve faster

BCD addition that results into a better overall performance for the arithmetic unit as shown in Section VII.

### V. EQUAL BLOCK SIZE CARRY SELECT ADDER STRUCTURE(EBS CSLA)

Carry select adder (CSLA) is used in many computational systems to alleviate the problem of carry propagation delay by independently generating multiple carries and then select a carry to generate the sum. But, CSLA is not area efficient because it uses multiple pairs of Ripple Carry Adders(RCA)

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

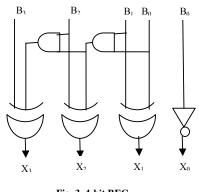

Fig. 3. 4-bit BEC

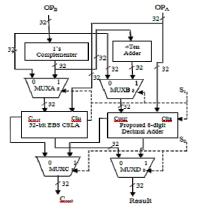

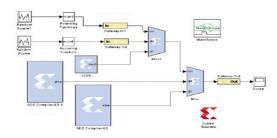

### VI. UNIFIED BINARY AND BCD ADDITION/SUBTRACTION UNIT

In this section, we discuss a 32-bit (8 BCD digits) wide unit that is capable of performing four different arithmetic operations based on two control signals  $S_1$  and  $S_0$ . The various functions for this unit are listed in Table III. The block diagram for the unit is shown in Figure 5. In addition to the control signals, the unit accepts two 32-bit (8 BCD digits) wide operands  $OP_A$  and  $OP_B$ . The unit consists of an inversion unit, a 32-bit binary adder, a block labeled "Ten Adder", the proposed 8-digit BCD adder, three 32-bit wide  $2 \times 1$  MUXs, and one 1-bit wide  $2 \times 1$  MUX. The inversion unit generates the one's complement of  $OP_B$  to be used in the binary subtraction operation.

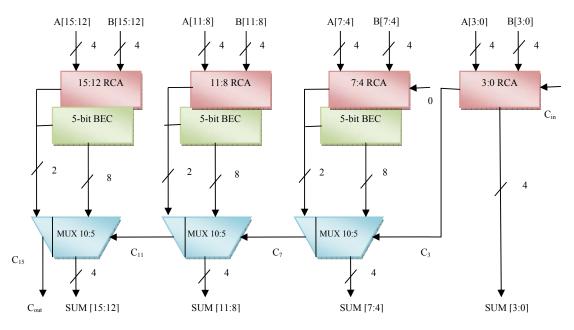

Fig. 4. 16-bit Equal Block Size Architecture for binary adder

to generate partial sum and carry by considering carry input Cin=0 and Cin= 1, then the final sum and carry are selected by the multiplexers(mux).

Binary to Excess-1 Converter (BEC) is used instead of RCA with  $C_{in} = 1$  in the equal block size CSLA (EBS) to achieve lower area and power consumption. The idea of this work is to use BEC instead of RCA with  $C_{in} = 1$ . The main advantage of this BEC logic comes from the lesser number of logic gates than the n-bit Full Adder (FA) structure. 4-bit BEC structure is shown in the fig. 3.

The structure of the 16-bit EBS is shown in fig. 4 which uses BEC for RCA to optimize area and power. Two 16-bit EBS structures are combined in carry ripple fashion to build 32-bit EBS unit. This is used for 32-bit binary adder in unified binary and decimal addition/subtraction unit.

Fig. 5 Unified binary and BCD addition/subtraction Unit TABLE III: FUNCTIONAL TABLE FOR THE UNIFIED BINARY AND BCD ADDITION/SUBTRACTION UNIT

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

| <b>S</b> <sub>1</sub> | $\mathbf{S}_{0}$ | Operation           |

|-----------------------|------------------|---------------------|

| 0                     | 0                | Decimal Addition    |

| 0                     | 1                | Binary Addition     |

| 1                     | 0                | Decimal Subtraction |

| 1                     | 1                | Binary Subtraction  |

As we have mentioned before, we compute the nine's complement by adding  $(1010)_2$  to the one's complement of the BCD digit and ignoring the last carry. Thus, to get the nine's complement of  $OP_B$  we feed the one's complement of OP<sub>B</sub> to the "Ten Adder" block which, in turn, adds (1010)<sub>2</sub> to the inverted bits of each BCD digit in OPB. Based on the control signal S<sub>1</sub>, MUXA selects between OP<sub>B</sub> or its one's complement. Also, MUXB chooses between OP<sub>B</sub> or its nine's complement. OP<sub>A</sub> is connected directly to the first input of the 32-bit EBS that is binary adder and to the first input of the proposed 8digit BCD adder. The input of the 32-bit EBS is driven by the output of MUXA, while the other input of the proposed 8-digit BCD adder is driven by the output of MUXB. The function of MUXC and MUXD is to choose between a binary (32-bit plus carry) result or a decimal (8-digit plus carry) result based on the control signal  $S_0$ .

## VII. SYNTHESIS REPORT AND COMPARISON

VerilogHDL is used to describe this proposed unified binary and decimal addition/subtraction unit. The code is optimized for FPGA synthesis at modular level to ensure best results in-terms of area and delay. This design has been synthesized and implemented using Xilinx ISE 13.4i design tools targeting on Xilinx Virtex 4 FPGA device. For comparison purpose with existing designs, we have targeted the 4VFX60FF672-12 Virtex 4 FPGA device and implemented a 32-bit wide unit. Synthesis reports for the proposed design are listed in Table IV, Table V.

## TABLE IV: TIMING SUMMARY OF UNIFIED BINARY AND BCD ADDITION/SUBTRACTION UNIT

| Timing Parameter                           | Proposed Unit |

|--------------------------------------------|---------------|

| Minimum Period                             | 3.011ns       |

| Maximum Frequency                          | 332.132MHz    |

| Minimum input arrival<br>time before clock | 3.999ns       |

| Maximum output required time after clock   | 3.793ns       |

| Gate Delay(Logic)                          | 1.161ns       |

| Net Delay(Route)                           | 1.850ns       |

TABLE V: HARDWARE RESOURCE UTILIZATION SUMMARY OF UNIFIED DESIGN

| Device Parameter              | Number Usage |

|-------------------------------|--------------|

| Number of Slices              | 243          |

| Number of Slice Flip<br>Flops | 286          |

| Number of 4 input<br>LUTs     | 443          |

| Number of bonded<br>IOBs      | 100          |

We extract the results for our design and compare them with the results for other designs, which are listed in Table VI. After comparing the results in Table VI, our design outperforms other designs in terms of speed. The delay obtained is 3.011 ns while the best delay among all other designs is 7.9 ns by M.Tyagi. Our design achieved 37.9% of speed improvement over M.Tyagi. The proposed design outperforms all other designs in terms of speed and most of the designs in terms of area.

TABLE VI: COMPARISON BETWEEN EXISTING DESIGNS AND OUR DESIGN

| Design      | Delay(ns) | Slices | LUTS |

|-------------|-----------|--------|------|

| Our Design  | 3.0       | 243    | 443  |

| M. Tyagi    | 7.9       | 280    | 530  |

| Sreehari    | 8.9       |        | 523  |

| Al-Khaleel  | 9.1       | 212    | 381  |

| Haller      | 10.0      | 305    | 584  |

| H. Calderon | 12.1      | 256    | 495  |

### VIII. CONCLUSION

A novel correction-free addition approach is being used in the design of BCD digit adder, thus achieved high performance and reduced area. This adder is then used in the design of 8-digit decimal adder with carry generation blocks. 32-bit EBS CSLA structure is designed for binary addition which has reduced area and less delay. These binary and decimal design units are then combined to build 32-bit unified binary and decimal addition/subtraction unit. A new way is used to achieve nine's complement for subtraction. This combined unit presented in this paper is synthesized, simulated and compared with existing designs. Implementation results show that our design achieved high speed and reduced area.

### REFERENCES

- H. Calderon, G. Gaydadjiev, and S. Vassiliadis, "Reconfigurable universal adder," in *IEEE International Conference on Application-specific Systems, Architectures* and Processors (ASAP2007), pp. 186–191, july 2007.

- [2] Osama A, Mohammad A, Zakaria , Christos A. P, Khaldoon. M, and Francis G. W "Fast Binary/Decimal Adder/Subtractor with a Novel Correction-Free BCD Addition" IEEE, pp 455-459, 2011

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

- [3] Sreehari. V, M. Kirthi Krishna, G. Prateek, S. Subroto, S. Bharat, and M. Srinivas, "A novel carry-look ahead approach to a unified bcd and binary adder/subtractor," in 21st International Conference on VLSI Design (VLSID 2008), pp. 547-552, jan. 2008.

- [4] M. Tyagi, A. Vashist, and K. K., "A novel hardware efficient reconfigurable 32-bit arithmetic unit for binary, bcd and floating point operands," *International Journal of Engineering Science and Technology*, vol. 3, pp. 4449–4464, may 2011

- [5] W. Haller, W. H. Li, M. R. Kelly, and H. Watter, "Highly Parallel Structure for Fast Cycle Binary and Decimal Adder Unit,"

Internetional Business Machines Corporation, US patent 2006/0031289, pp. 1–8, Feb 2006 [6] H. Fischer and W. Rohsaint, "Circuit Arrangement for

[6] H. Fischer and W. Ronsaht, Circuit Arrangement for Adding or Subtracting Operands Coded in BCD-Code or Binary-Code," Siemens Aktiengesellschaft, US patent 5146423, pp. 1–9, Sep 19

- [7] I. S. Hwang, "High-Speed Binary and Decimal Arithmetic Logic Unit," *American Telephone and Telegraph Company*, *AT & T Bell Laboratories*, US patent 4866656, pp. 1–11, Sep 1989.92.

- [8] F. Y. Busaba, C. A. Krygowsky, W. H. Li, E. M. Schwarz, and S. R. Carlough, "The IBM z900 Decimal Arithmetic Unit," *Conference Record of the 35th Asilomar Conference* on Signals, Systems and Computers, pp. 1353–1339, Sep 2001.

- [9] J. Moskal, E. Oruklu, and J. Saniie, "Design and synthesis of a carryfree signed-digit decimal adder," in *IEEE International Symposium on Circuits and Systems (ISCAS* 2007), pp. 1089-1092, may 2007.

- [10] H. Thapliyal and M. B. Srinivas, "The New BCD Subtractor and its Reversible Logic Implementation," *Lecture Notes in Computer Science, Springer-Verlag*, pp. 466–472, 2006.

- [11] W. Haller, U. Krauch, and H. Watter, "Combined Binary/Decimal Adder Unit," *Internetional Business Machines Corporation*, US patent 5928319, pp. 1–9, Jul 1999.

### DESIGN AND SIMULATION OF UART PROTOCOL BASED ON VERILOG

### <sup>1</sup>B.JEEVAN & <sup>2</sup>M.NEERAJA

<sup>1,2</sup>Dept of E.I.E, KITS, Warangal, Andhra Pradesh, India

Abstract—UART (Universal Asynchronous receiver Transmitter) is a kind of serial communication protocol; mostly used for short-distance, low speed, low-cost data exchange between computer and peripheral. The UART takes bytes of data and transmits the individual bits in a sequential fashion. At the destination, a second UART re-assembles the bits into complete bytes. The UART allows the devices to communicate without the need to be synchronized. UART includes three kernel modules which are generator, receiver and transmitter. The UART implemented with VERILOG language can be integrated into FPGA. The simulation results with Xilinx are completely consistent with the UART protocol.

Keywords- UART, asynchronous serial communication, Xilinx

### I. INTRODUCTION

Asynchronous serial communication has advantages of less transmission line, high reliability, and long transmission distance, therefore is widely used in data exchange between computer and peripherals. Specific interface chip will cause waste of resources and increased cost. This situation results in the requirement of realizing the whole system function in a single or a very few chips. Integrate the similar function module into FPGA. This paper uses VERILOG to implement the UART core functions and integrate them into a FPGA chip.

Basic UART communication needs only two signal lines(RXD,TXD) to complete full-duplex data communication.TXD is the transmit side, the output of UART; RXD is the receiver, the input of UART. Logic 1(high) logic 0 (low) are two basic features of UART. When the transmitter is idle, the data line is in the high logic state otherwise in low logic state. When a word is given to the UART for asynchronous transmission, a bit called the "Start Bit" is added to the beginning of each word that is to be transmitted. The start bit is used to alert the receiver that a word of data is about to sent.

After the Star Bit, the individual data bits of the word are sent, with the Least Significant Bit(LSB) being sent first. Each bit is transmitted for exactly same amount of time, and the receiver looks at approximately halfway through the period assigned to each bit to determine if the bit is 1 or 0.

The sender does not know when the receiver has "looked" at the value of the bit. The sender only knows when the clock says to begin transmitting the next bit of the word. When the entire data word has been sent, the transmitter may add a Parity Bit that the transmitter generates. The Parity Bit may be used by the receiver to perform simple error checking (both the sender and receiver must agree on whether a Parity Bit may use or not) and when the receiver has received all of the bits in the data word then receiver looks for stop bit.

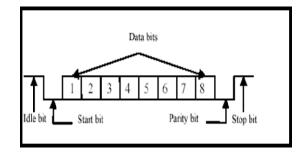

If the Stop Bit does not appear, the UART considers the entire word be garbled and will report Framing Error. When the another word is ready for transmission, the start bit for the new word can be sent as soon as the stop bit for the previous word has been sent. The UART frame format is show in fig. 1.

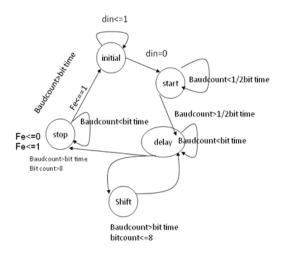

### Fig. 1 UART Frame Format

### **II. IMPLEMENTATION OF UART**

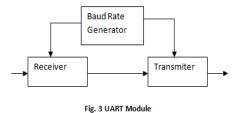

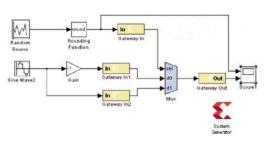

In this paper Top to Down design method is used. The UART module is divided into three sub-modules: the transmitter module, receiver module and baud rate generator, shown in fig. 3

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

### A.BAUD RATE GENERATOR

THE Baud Rate Generator is used to produce used to produce a local clock signal which is much higher than the baud rate to control the UART receiver and transmit. The baud rate generator is actually a frequency divider. The frequency factor is calculated according to the given system clock frequency and requested baud rate. Assume that the system clock is 50MHZ, baud rate is 9600bps.Therefore the frequency coefficient (M) of baud rate generator is:

### M=50\*10^6/9600Hz=5200

### B. TRANSMIT MODULE

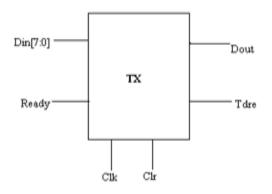

The UART transmit module converts the bytes into serial bits according to the basic frame format and transmits those bits through TXD. The transmit module is to convert the sending 8-bit parallel data into serial data ,adds start bit at the head of the data as well as the parity and stop bits at the end of the data. The schematic of a transmitter module is as shown in the figure below.The 8-bit ASCII data is supplied in to the module via. Din[7:0]. The 'ready'line is HIGH whenever the module is ready to transmit data, 'trde' line is HIGH when the transmission of data is complete i.e. the stop bit is transmitted. 'CLR' is used to reset all the parameter, the 'clk' provides timing information regarding the flow of data bits. Serial output data is transmitted via. Dout line.

#### Fig.4 Transmitter module

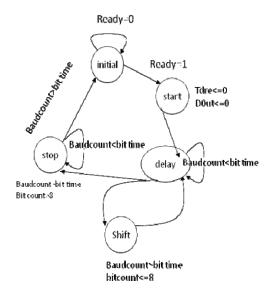

The transmitter only needs to output 1 bit every clock cycles(the transmitting clock frequency generated by baud rate generator). The order follows 1 start bit , 8 data bits ,1 parity bit and 1 stop bit. The parity bits is determined according to the number of logic 1 in 8 data bits. Then the parity bits is output. Finally 1 is output as the stop bit. Fig. 5 shows the transmit module state diagram

Fig. 5 UART Transmiter State Machine This state machine has 5 states : MARK(idle), START(start bit), DELAY, SHIFT(shift), STOP(stop bit).

- *MARK Status*: When the UART is reset, the state machine will be in this state, the UART transmitter has been waiting a data frame sending command READY. When READY=1, the state machine transferred to START, get ready to send a start bit.

- *START Status* : In this state, sends a logic 0 signal to the TXD for one bit time width, the start bit. Then the state machine transferred to DELAY state.

- *DELAY Status*: when the state machine is in this state, waiting for counting baud rate clock then entering into the SAMPLE to sample the data bits .at the same time determining whether the collected data bit length has reached the data frame length. If reaches, it mens the stop bits arrives.inthis design it is 8, which corresponds to the 8-bit data formate of UART

- *SHIFT Status* : In this state , the state machine realizes the parallel to serial converision of outgoing data. Then immediately return to DELAY state

- *STOP Status*: when the data frame transmit is completed, the state machine transferred to this state, and sends 5200 baud clock cycle logic 1 signal, that is 1 stop bit. then the state turns to mark state after sending the stop bitand waits for another data frame transmit

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

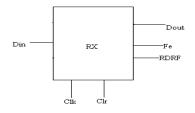

### C.RECEIVER MODULE

The UART receiver module is used to receiver the serial signals at RXD, and convert them into parallel data. The receiver module design is largely complementary to that of the transmitter design. The schematic of a receiver module is as shown in the figure below. The 8-bit ASCII data is revceived by the module via. Din. The 'rdrf'line is HIGH whenever the module has received the stop bit, 'fe' line is HIGH when there is an error in reception of the frame. However for simplcity purpose in this design the 'fe' line is HIGH only when there is an error in reception of the STOP bit. 'CLR' is used to reset all the parameters, the 'clk' provides timing information regarding the flow of data bits.

Serial output data is transmitted via. Dout[7:0] line. The receiver module receives data from RXD pin. RXD jumps into logic 0 from logic 1 can be regarded as the beginning of the data frame . The receiver module receives data from RXD pin. RXD jumps into logic 0 from logic 1 can be regarded as the beginning of the data frame. The receiver module receives data from RXD pin.

#### Fig 6.Receiver Module

The receiver module receives data from RXD pin. RXD jumps into logic 0 from logic 1 can be regarded as the beginning of the data frame. As stated earlier, the parameters used in design of an Rx module remains the same. A new parameter namely 'half\_bit\_time' which represents half of the bit time. Due to the delay in transmission of data, the start bit appears only after half the bit time has elapsed. Once the start bit been identified, from the next bit, being to count the rising edge of the baud clock, and sample RXD when counting. Each sampled value of the logic level is deposited in the register rbuf[7,0] by order.when the count equals 8, all the data bits are surely received, also the 8 serial bits are converted into parallel data. The receiver finite state manchine diagram is show in fig. 7

Fig.7 UART Receiver State Machine

The state machine includes five states: MARK(wating for startbit),START(findmidpoint),DELAY,SHIFT(shift) ,STOP(receving stop bit)

- *MARK status:* when the UART receiver is reset, the receiver state machine will be in this state.

- *START Status:* For asynchronous serial signal, in the order to detect the correct signal each time, and minimize the total error in the later data bits detection. In this state, the task is to find midpoint of each bit through the start bit.

- DELAY Status: Similar with the Transmit \_DELAY of UART transmit state machine

- *SHIFT Status:* After sampling the state machine transfer to DELAY state unconditionally, waits for the arrival of next start bit.

- *STOP Status:* Stop bit is either 1 or 1.5,or 2. State machine doesn't detect RXD in STOP, but output frame receiving done signal. After the stop bit, state machine turns back to START state, waiting for the next frame start.

### **III. SIMULATION OF MODULES**

The simulation software is Xilinx. During simulation, the system clock is set to 50MHZ, and baud rate is set to 9600bps. And the selected device is Sparton 3E FPGA.

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

### A. Transmitter Simulation

| ete | line Ber   | 11.125 13                |     | • Frinter | 31               | N E        | Interval.) | 78.3 m            | itet    |        | hi     | tj     |                    |

|-----|------------|--------------------------|-----|-----------|------------------|------------|------------|-------------------|---------|--------|--------|--------|--------------------|

|     | Ĭu+        | 0 px 361.84<br>14 125 px | n I | 7.68 cm   | \$1. <u>17</u> u | 655. JE 14 | 819.2 m    | 913. <b>J</b> ¥ u | L IŞ mı | 13, 11 | 1.9 ո  | 1.84 m | I.B <sub>.</sub> m |

| 2   | hdle.      |                          | UM  | UNU       | Ulini            | TUUU       | u u u u U  |                   |         |        | Nu u u |        | mu                 |

|     | rasit      | ЛІІ                      |     |           |                  |            |            |                   |         |        |        |        |                    |

| è   | anit_end_p | лл                       |     |           |                  |            |            |                   |         | J      |        |        |                    |

| 1   | tobat      |                          |     |           |                  |            |            | 100000            |         |        |        |        |                    |

| ż   | tel        |                          |     |           |                  |            |            |                   | 1111    |        |        |        |                    |

| 2   | tri ins    |                          |     |           |                  |            |            |                   |         |        |        |        |                    |

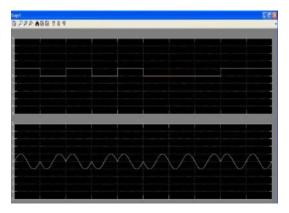

### **Fig.8 Simulation Results of Transmitter**

Fig.8 shows the Transmitter simulation. The present\_state indicates the current state of the state machine. It traverses from IDLE to STOP state. The data input can be seen on din and corresponding serial output is given on dout. Since  $parity_en = 1$ , parity bit is appended to data.

B. Receiver Simulation

**Fig.9 Simulation Results of Receiver**

Fig. 9 shows the Receiver simulation. The state transitions are similar to transmitter. The serial data input comes on sin and output data is dout. The data is sampled when data rx done = '1'.

### **IV. CONCLUSION**

This design uses VERILOG as design language to achieve the modules of UART. Using XILINX software, Saptron 3E FPGA to complete simulation and test . The results are stable and reliable data transmission with some reference value and great flexibility, high integration.

### REFERENCES

- [1]. Zou, Jie Yang, Jianning Design and Realization of UART Controller Based on FPGA

- [2]. Liakot Ali, Roslina Sidek, Ishak Aris, Alauddin Mohd. Ali, Bambang Sunaryo Suparjo. Design of a micro - UART for SoC application [J].In: Computers and Electrical Engineering 30 (2004) 257-268

- [3]. HU Hua, BAI Feng-e. Design and Simulation of UART Serial Communication Module Based on Verilog -HDL[J]. J Isuanj I Yu Xianda Ihua 2008 Vol. 8

- [4]. Bhaskar, J. A Verilog HDL Primer -Pearson Education. 2001[5] Palnitkar, Samir. Verilog HDL A Guide to Digital Design and Synthesis-.

- [6] Smith, J. Douglas. HDL design

### A FAST WALLACE MULTIPLIER USING PARRLLEL PREFIX ADDER WITH REDUCED COMPLEXITY

### <sup>1</sup>S.V.KRISHNA RAO, <sup>2</sup>V.NEEHARIKA & <sup>3</sup>V.DEEPIKA

<sup>1,2,3</sup>KITS, Warangal, Andhra Pradesh, India

Abstract—Wallace high-speed multipliers use full adders and half adders in their reduction phase. Half adders do not reduce the number of partial product bits. Therefore, minimizing the number of half adders used in a multiplier reduction will reduce the complexity. A modification to the Wallace reduction is presented that ensures that the delay is the same as for the conventional Wallace reduction. The modified reduction method greatly reduces the number of half adders; producing implementations with 80 percent fewer half adders than standard Wallace multipliers, with a very slight increase in the number of full adders. Wallace multipliers perform in parallel, resulting in high speed. It uses full adders and half adders in their reduction phase. Reduced Complexity Wallace multiplier will have fewer adders than normal Wallace multiplier. In both multipliers, at the final stage, Carry propagating adder is used, which contributes to delay. This paper proposes, employing parallel prefix adders (fast adders) at the final stage of Wallace multipliers to reduce the delay.

Keywords-High speed multiplier Wallace multiplier, Dadda multiplier, Parallel prefix adder, multiplier delay

### 1. INTRODUCTION

The well-known Wallace high-speed multiplier uses carry save adders to reduce an N-row bit product matrix to an equivalent two row matrix that is then summed with a carry propagating adder to give the product [1]. It is a fully parallel version of the multiplier used in the IBM Stretch computer [2]. The carry save adders are conventional full adders whose carries are not connected, so that three words are taken in and two words are output. As described more clearly in [3], the Wallace multiplier also uses half adders in the reduction phase. This paper presents a modified design that greatly reduces the number of half adders in Wallace multipliers.

This section describes the notation and terminology used in this paper. Throughout this paper, both input operands are assumed to be N-bit unsigned words. Section 2 reviews the two main previous multiplier reduction approaches (Wallace and Dadda). Section 3 presents the modified Wallace approach to multiplier reduction. Section 4 presents the results for multipliers of sizes ranging from 8 to 64 bits. Finally, Section 5 summarizes the conclusions.

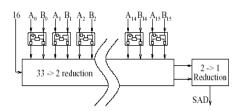

The multipliers involve three distinct phases. First, the matrix of partial products is formed. These are simply the AND of each bit of the first operand with each bit of the second operand. This forms an N-row skewed matrix of partial product terms where each row contains N single bit terms. In the second phase, the partial product matrix is reduced with carry save adders to a height of two terms. Finally, in the third phase, the two terms are added with a carry propagating adder to generate the product. It is usually assumed that a carry look ahead adder is used for the addition.

This paper is concerned with the second phase where the N rows of partial product bits are reduced to two rows. In this phase, the Wallace approach uses several stages of full and half adders as carry save adders that are arranged to maximize the reduction at each stage. Full adders take in three bits and output two bits for a net reduction of one bit per full adder. Half adders take in two bits and output two bits. They simply shift the position of one of the bits. For an Nbit by N-bit Wallace multiplier, the number of half adders is roughly proportional to N1:5 which results in the second phase of Wallace multipliers being more complex and larger than that of Dadda multipliers which use N - 1 half adders.

The Dadda dot notation for the second stage of multiplier (array reduction) [3] is used here. The multipliers, in this paper, are for unsigned operands, but the same process is used for multipliers for two's complement operands by inverting the bit products along the bottom and top edge of the initial bit product array from the center column to the next to the leftmost column and adding a one to the first column to the left of the center column [4]. Adding the one can be done using a special half adder that computes the sum of the two data plus one. It is the same complexity as a conventional half adder. Thus, the complexity of the reduction for two's complement operands.

Arithmetic & Logic Unit (ALU) is the core unit of a processor. It contains units for arithmetic operations. It plays a vital role in computation time of the processor. In applications like Digital Signal Processing (DSP), multiplication operation is more frequent. Reducing delay in the multiplier reduces the overall computation time.

Wallace multiplier is one of the fast multipliers available. It works on the basis of "Acceleration of addition of summands.. The final two rows are summed with a carry propagating adder. A direct implementation requires a (2N-2) bit carry propagating adder, where N – number of bits of operands. Carry Propagating Adder (CPA) takes long

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1

time as the carry need to get propagated until the last adder. In this proposal, a fast adder is implemented at the final stage to get better performance. Employing the parallel prefix adder (fast adder) at the final stage of Wallace multiplier to reduce the delay.

### 2. PREVIOUS APPROACHES

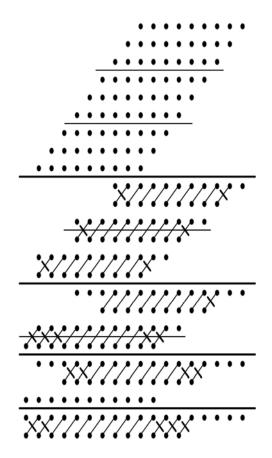

### • 2.1 WALLACE REDUCTION APPROACH

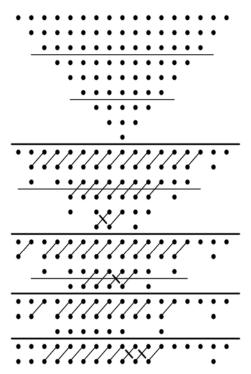

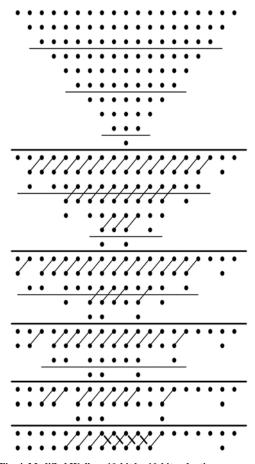

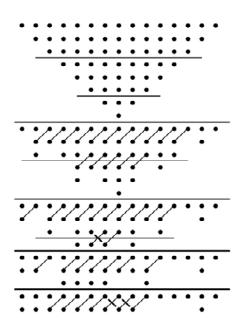

For the conventional Wallace reduction method, once the partial product array (of N2 bits) is formed, adjacent rows are collected into non overlapping groups of three. Each group of three rows is reduced by 1) applying a full adder to each column that contains three bits, 2) applying a half adder to each column that contains two bits, and (3) passing any single bit columns to the next stage without processing. This reduction method is applied to each successive stage until only two rows remain. The final two rows are summed with a carry propagating adder. This process is illustrated by the conventional 9-bit by 9-bit Wallace multiplier shown in Fig. 1. Light lines show the three row groupings. The reduction is performed in four stages (each with the delay of one full adder) with a total of 50 full adders and 21 half adders. The third phase will require a 13bit wide adder.

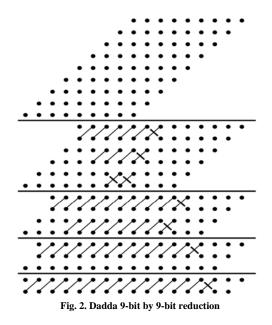

### • 2.2 DADDA REDUCTION APPROACH

In contrast to the Wallace reduction, the Dadda method [3] does the least reduction necessary at each stage. To determine how much reduction is required, the maximum height of each stage is calculated by working back from the final stage. It has a height of two rows. Each preceding stage height can be no larger than (3. successor height/2) where [x] denotes the integer portion of x. This gives 2, 3, 4, 6, 9, 13, 19, 28, 42, 63, etc., as the maximum heights for the various stages. The Dadda reduction then uses just enough full and half adders to achieve the limits. A 9bit by 9-bit Dadda multiplier is shown in Fig. 2. The reduction is performed in four stages (the same as the Wallace reduction) with a total of 48 full adders and 8 half adders. The third phase will require a 16-bit wide adder. The Dadda multiplier uses two fewer full adders and 13 fewer half adders in the second phase reduction than the Wallace multiplier and requires a slightly larger carry propagating adder in the third phase as a result.

### **3 MODIFIED WALLACE REDUCTION**

## • 3.1 MODIFIED WALLACE REDUCTION APPROACH

This section presents the modified Wallace method for educing the partial product array (the second phase). As shown in Fig. 3, the initial partial product array of the first phase is changed by shifting bits in the left half of the array upward to form an inverted pyramid array (the partial product generation method is the same, no data are changed; only their vertical position is shifted).

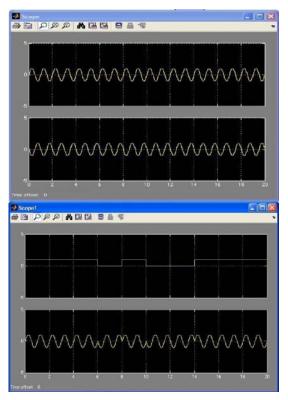

Fig.1. Conventional Wallace 9-bit by 9-bit reduction

In the second phase, the modified Wallace approach is similar to the conventional Wallace approach in that it uses as many full adders as possible, but different in that it only uses half adders when necessary to ensure that the number of reduction stages is the same as for a conventional Wallace multiplier.

The modified Wallace reduction method divides the matrix into three row groups and uses full adders for each group of three bits in a column like the conventional Wallace reduction. A group of two bits in a column is not processed, that is, it is passed on to the next stage (in contrast to the conventional Wallace reduction). Single bits are passed on to the next stage as in the conventional Wallace reduction. The only time half adders are used is to ensure that the number of stages of the modified Wallace multiplier does not exceed that of a conventional Wallace multiplier. For some cases, half adders are only used in the final stage of reduction.

International Conference on Electronics and Communication Engineering (ICECE) -16th Sept, 2012, Pune- ISBN: 978-93-82208-18-1