## Interscience Research Network

## **Interscience Research Network**

**Conference Proceedings - Full Volumes**

**IRNet Conference Proceedings**

2-12-2012

## Proceedings of International Conference on Electrical, Electronics & Computer Engineering

Prof.Srikanta Patnaik Mentor IRNet India, patnaik\_srikanta@yahoo.co.in

Follow this and additional works at: https://www.interscience.in/conf\_proc\_volumes

Part of the Computer Engineering Commons, and the Electrical and Electronics Commons

#### **Recommended Citation**

Patnaik, Prof.Srikanta Mentor, "Proceedings of International Conference on Electrical, Electronics & Computer Engineering" (2012). *Conference Proceedings - Full Volumes*. 48. https://www.interscience.in/conf\_proc\_volumes/48

This Book is brought to you for free and open access by the IRNet Conference Proceedings at Interscience Research Network. It has been accepted for inclusion in Conference Proceedings - Full Volumes by an authorized administrator of Interscience Research Network. For more information, please contact sritampatnaik@gmail.com.

# Proceedings of International Conference on ELECTRICAL, ELECTRONICS & COMPUTER ENGINEERING

# (ICEECE-2012) 12<sup>th</sup> February, 2012 AHMEDABAD, India

# Interscience Research Network (IRNet) Bhubaneswar, India

## **Editorial**

Although the discipline like electrical engineering has narrated academic maturity in the last decades, but the limitations of the non renewable energy sources, turbulence and disturbances in the energy propagation cascades various insightfulness and stimulation in post classical electrical era. Evidence shows that there are phenomenal supplements in power generation and control after the introduction of Energy Management System (EMS) supported by Supervisory Control and Data Acquisition (SCADA). As there is increasing focus on strengthening the capacity of the power houses with the existing resources or constraints some new dimensions like FACTS, Optimal System Generation, High Voltage DC transmission system, Power Generation, economics of generation, fault analysis in power systems are emerging. Since the world is suffering with water, food, and energy crisis, energy consumption has social relevancy.

Keeping view of the ongoing energy and power issues many action research can be initiated by the research fraternity of this domain. The conference is a thought provoking outcome of all these interrelated facts.

In the quest of making this earth a better place to live we have to make a strong hold upon sustainable energy source. Sustainable energy sources include all renewable energy sources, such as hydroelectricity, solar energy, wind energy, wave power, geothermal energy, bioenergy, and tidal power. It usually also includes technologies designed to improve energy efficiency. Energy efficiency and renewable energy are said to be the twin pillars of sustainable energy. Renewable energy technologies are essential contributors to sustainable energy as they generally contribute to world energy security, reducing dependence on fossil fuel resources, and providing opportunities for mitigating greenhouse gases.

Let me highlight some of the recent developments in Electronics discipline. The new integrated devices did not find a ready market. Users were concerned because the individual transistors, resistors, and other electronic circuit components could not be tested individually to ensure their reliability. Also, early integrated circuits were expensive, and they impinged on the turf that traditionally belonged to the circuit designers at the customer's company. Again, Bob Noyce made a seminal contribution. He offered to sell the complete circuits for less than the customer could purchase individual components to build them. (It was also significantly less than it was costing us to build them!) This step opened the market and helped develop the manufacturing volumes necessary to reduce manufacturing costs to competitive levels. To this day the cost reductions resulting from economies of scale and newer high-density technology are passed on to the user—often before they are actually realized by the circuit manufacturer. As a result, we all know that the high-performance electronic gadget of today will be replaced with one of higher performance and lower cost tomorrow.

The integrated circuit completely changed the economics of electronics. Initially we looked forward to the time when an individual transistor might sell for a dollar. Today that dollar can buy tens of millions of transistors as part of a complex circuit. This cost reduction has made the technology ubiquitous—nearly any application that processes information today can be done most economically electronically. No other technology that I can identify has undergone such a dramatic decrease in cost, let alone the improved performance that comes from making things smaller and smaller. The technology has advanced so fast that I am amazed we can design and manufacture the products in common use today. It is a classic case of lifting

ourselves up by our bootstraps—only with today's increasingly powerful computers can we design tomorrow's chips.

The mushrooming growth of the IT industry in the 21<sup>st</sup> century determines the pace of research and innovation across the globe. In a similar fashion Computer Science has acquired a path breaking trend by making a swift in a number of cross functional disciplines like Bio-Science, Health Science, Performance Engineering, Applied Behavioral Science, and Intelligence. It seems like the quest of Homo Sapience Community to integrate this world with a vision of Exchange of Knowledge and Culture is coming at the end. Apparently the quotation "Shrunken Earth, Shrinking Humanity" holds true as the connectivity and the flux of information remains on a simple command over an internet protocol address. Still there remains a substantial relativity in both the disciplines which underscores further extension of existing literature to augment the socio-economic relevancy of these two fields of study. The IT tycoon Microsoft addressing at the annual Worldwide Partner Conference in Los Angeles introduced Cloud ERP (Enterprise Resource Planning,) and updated CRM (Customer Relationship Management) software which emphasizes the ongoing research on capacity building of the Internal Business Process. It is worth mentioning here that Hewlett-Packard has been with flying colors with 4G touch pad removing comfort ability barriers with 2G and 3G. If we progress, the discussion will never limit because advancement is seamlessly flowing at the most efficient and state-of-the art universities and research labs like Laboratory for Advanced Systems Research, University of California. Unquestionably apex bodies like UNO, WTO and IBRD include these two disciplines in their millennium development agenda, realizing the aftermath of the various application projects like VSAT, POLNET, EDUSAT and many more. 'IT' has magnified the influence of knowledge management and congruently responding to social and industrial revolution.

It's my pleasure to welcome all the participants, delegates and organizer to this international conference. In the process of organizing this conference IRNet family members have shown their commitment and dedication. I sincerely thank all the authors for their invaluable contribution to this conference. I am indebted towards the reviewers and Board of Editors for their generous gifts of time, energy and effort.

Editor-in-Chief

**Prof. (Dr.) Srikanta Patnaik** President, IRNet India and Chairman IIMT Intersceince Campus, Bhubaneswar Email: iceee.ahmedabad@gmail.com **SECTION-I** Electrical and Electronics Engineering

## Analysis and Simulation of Uniform Step Asymmetrical Multilevel Inverter

Hina Chandwani, Dhaval Patel & Himanshu N Chaudhari

Dept. of Electrical Engineering, The M.S.University of Baroda, Vadodara, India

Abstract - This paper presents cascaded multilevel inverter(MLI) approach for high voltage and high power output applications. It is based on the series connection of the H-bridge inverter cells powered by the supplies which are in GP with different ratios like 2,3,4etc. The proposed configuration is shown for 15 level and 27 level inverters, having inherent advantages of the cascade H-bridge inverters. Structural and operational characteristics are discussed. Simulation using Matlab Simulink is done to verify the performance. Simulation result for this proposed scheme are shown in this paper .

Keywords - Asymmetrical Multilevel Inverter, MATLAB simulink, Symmetrical step control techniques, , Total harmonic distortion(THD).

#### I. INTRODUCTION

The emergence of multilevel inverters has been increased since last decade. These new types of inverters are suitable for high voltage and high power application due to their ability to synthesize waveforms with better harmonic spectrum. Numerous topologies have been introduced and widely studied for utility and drive applications. Amongst these topologies, the multilevel cascaded inverter was introduced in Static VAR compensation and drive systems.

The multilevel inverter [MLI] is a promising inverter topology for high voltage and high power applications. This inverter synthesizes several different levels of DC voltages to produce a staircase (stepped) that approaches the pure sine waveform. It has high power quality waveforms, lower voltage ratings of devices, lower harmonic distortion, lower switching frequency and switching losses, higher efficiency, reduction of dv/dt stresses. It gives the possibility of working with low speed semiconductors in comparison with the two-levels inverters. Numerous of MLI topologies and modulation techniques have been introduced and studied extensively. But most popular MLI topology is Diode Clamp, Flying Capacitor and Cascaded Multilevel Inverter (CMLI). In this paper we use a CMLI that consist of some H-Bridge inverters and with un-equal DC named as Asymmetric Cascaded Multilevel Inverter (ACMLI). It is implemented with

uniform step because this inverter is more modular and simple in construction.

There are many modulation techniques to control this inverter, such as Selected Harmonics Elimination or Optimized Harmonic Stepped-Waveform (OHSW), Space Vector PWM (SVPWM) and Carrier-Based PWM (CBPWM), Symmetrical step control. A symmetrical step control is used for multilevel inverter because of its advantages of simple logic and easy implementation.

#### Asymmetrical Multi Level Inverter(Acmli) :

This method eliminates the excessively large number of bulky transformers required by conventional multi level inverters, the clamping diodes required by diode clamped multilevel inverters, and the flying capacitors required by flying capacitor multilevel inverters. This method consists a series connection of multiple H bridge inverters. Each H-bridge inverter has the same configuration as a typical single-phase fullbridge inverter. This method introduces the idea of using separate DC sources to produce an AC voltage waveform. Each H bridge inverter is connected to its own DC source. By cascading the output voltage of each H-bridge inverter, a stepped voltage waveform is produced. If the number of H-bridges is N, the voltage output is obtained by summing the output voltage of

International Conference on Electrical, Electronics & Computer Engineering (ICEECE)- 11th February, 2012 - Ahmedabad

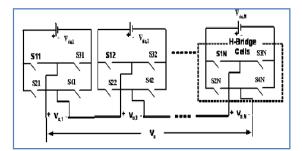

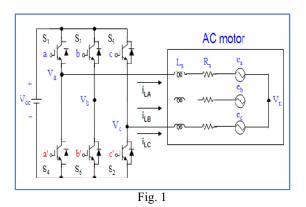

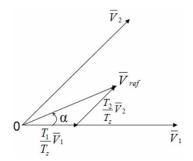

bridges as shown in equation. Fig. 1 shows configuration of ACMLI of single-phase.

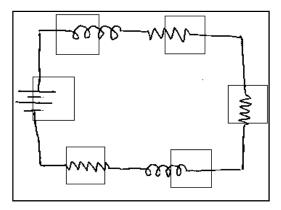

Fig. 1 : Single-phase cascaded multilevel inverter.

If ACMLI has N H-Bridges, The output voltage could be expressed as ;

$$Vo(t) = Vo1(t) + Vo2(t) + \dots + VoN(t)$$

(1)

Where, Vo1(t), Vo2(t), ..... VoN(t) are the output of individual H-bridge.

In the CMLI, the DC voltage may or may not be equal. If DC voltage given to all H-bridges is same that CMLI is called SCMLI. If DC voltage is different then it is called ACMLI.

In ACMLI DC voltage with ratio binary and ternary are the most popular. In binary progression within H-Bridge inverters , the DC voltages having ratio 1: 2: 4: 8. . : 2N and the maximum voltage output would be  $(2^{N-1})$  V dc and the voltage levels will be  $(2^{N+1}-1)$ . While in the ternary progression the amplitude of DC voltages having ratio 1: 3: 9: 27. . : 3N and the maximum output voltage reaches to  $((3^{N-1})/2)$  V dc and the voltage levels will be $(3^{N})$ .

#### **II. OPERATION CHARACTERISTICS:**

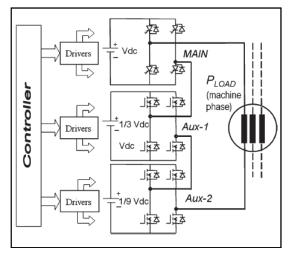

One advantage of this particular Asymmetric CMLI is that most of the power delivered to the load by H Bridge having the highest DC source called "MAIN" bridge. The example of Fig. 2 shows the simulated power distribution in one phase of the 27-level MLI, as a function of output voltage. At full power, around 81% of the real power is delivered by the Main H-bridge, but only 16% from the Aux-1 bridges and approximately 3% of the total power from Aux-2 bridges.

#### III. SYMMETRICAL STEP CONTROL TECHNIQUE:

Among other modulation, Symmetrical step control strategies are the most popular methods used in CMLI, because they are easily implemented. Basic principle of Symmetrical step control strategies is all output steps are Symmetrical. Circuits are simulated in MATLAB/SIMULINK. For switching to the bridge switches in matlab simulink pulse generators are used. The outputs for different bridges are shown in tables.

#### TABLE I

#### VOLTAGE LEVELS OF EACH BRIDGE AND OUTPUT FOR 7 LEVEL ACMLI

| Bridge<br>1(2v) | Bridge<br>2(1v) | Voltage(amplitude) |

|-----------------|-----------------|--------------------|

| -2v             | -1v             | -3V                |

| -2v             | 0               | -2v                |

| 0               | -1v             | -V                 |

| 0               | 0               | 0                  |

| 0               | 1v              | V                  |

| 2v              | 0               | 2v                 |

| 2v              | 1v              | 3v                 |

#### TABLE II

## VOLTAGE LEVELS OF EACH BRIDGE AND OUTPUT FOR 15 LEVEL FOR HALF CYCLE

| Bridge<br>1(4V) | Bridge<br>2(2V) | Bridge<br>3(V) | Voltage(amplitude) |

|-----------------|-----------------|----------------|--------------------|

| 0               | 0               | 0              | 0                  |

| 0               | 0               | 1 <b>v</b>     | V                  |

| 0               | 2v              | 0              | 2v                 |

| 0               | 2v              | 1 <b>v</b>     | 3v                 |

| 4v              | 0               | 0              | 4v                 |

| 4v              | 0               | 1v             | 5v                 |

| 4v              | 2v              | 0              | 6v                 |

| 4v              | 2v              | 1 <b>v</b>     | 7v                 |

#### TABLE III

# VOLTAGE LEVELS OF EACH BRIDGE AND OUTPUT FOR 9 LEVEL FOR HALF CYCLE

| Bridge<br>1(3v) | Bridge<br>2(1v) | Voltage<br>(amplitude) |

|-----------------|-----------------|------------------------|

| 0               | 0               | О                      |

| 0               | 1v              | V                      |

| 3v              | -1v             | 2v                     |

| 3v              | 0               | 3v                     |

| 3v              | 1v              | 4v                     |

#### TABLE IV

## VOLTAGE LEVELS OF EACH BRIDGE AND OUTPUT FOR 27 LEVEL FOR HALF CYCLE

| Bridge<br>1(9v) | Bridge<br>2(3v) | Bridge<br>3(v) | Voltage<br>(amplitude) |

|-----------------|-----------------|----------------|------------------------|

| 0               | 0               | 0              | 0                      |

| 0               | 0               | 1v             | V                      |

| 0               | 3v              | -1v            | 2v                     |

| 0               | 3v              | 0              | 3v                     |

| 0               | 3v              | 1v             | 4v                     |

| 9v              | -3v             | -1v            | 5v                     |

| 9v              | -3v             | 0              | 6v                     |

| 9v              | -3v             | 1v             | 7v                     |

| 9v              | 0               | -1v            | 8v                     |

| 9v              | 0               | 0              | 9v                     |

| 9v              | 0               | 1v             | 10v                    |

| 9v              | 3v              | -1v            | 11v                    |

| 9v              | 3v              | 0              | 12v                    |

| 9v              | 3v              | 1v             | 13v                    |

Here TABLE I and TABLE II are having binary GP ratio for two bridges(7 level) and three bridges (15 level) respectively. Table III and Table IV are corresponding to ternary GP ratio for two bridges(9 level) and three bridges (27level) respectively. For symmetrical step control every level has duration of  $\pi/8$  in 7 level inverter and for 27 level it will be  $\pi/28$ .

#### **IV. SIMULATION:**

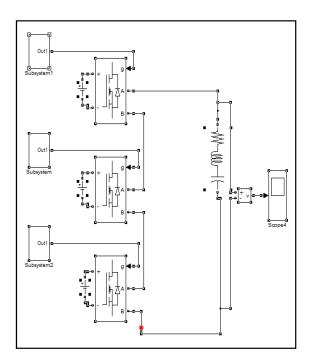

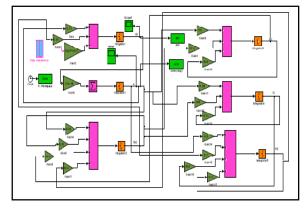

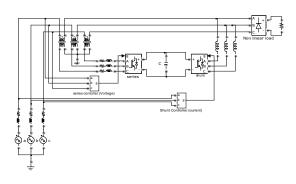

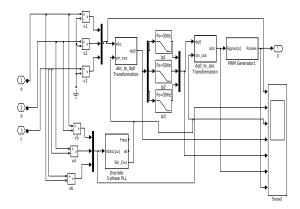

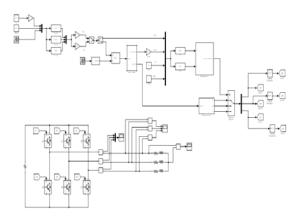

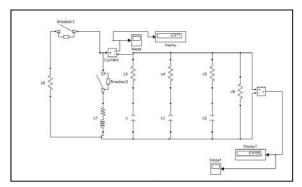

For simulation of 15 level and 27 level Asymmetrical multi level inverter the model is same but the switching states and sources of power are different.

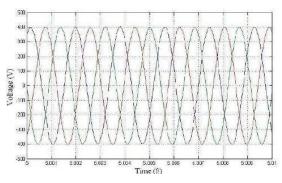

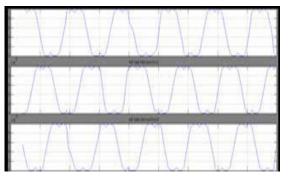

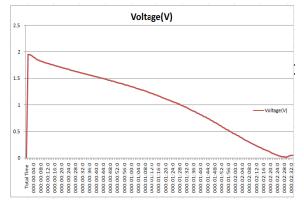

Fig. 3 : Simulink model of Asymmetrical CMLI with N=3,

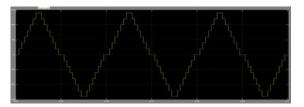

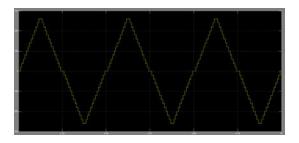

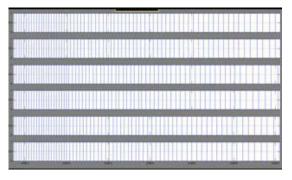

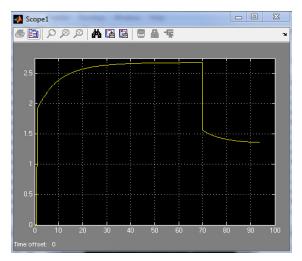

Fig. 4 : 15 level Asymmetrical Multi Level Inverter Output for ACMLI

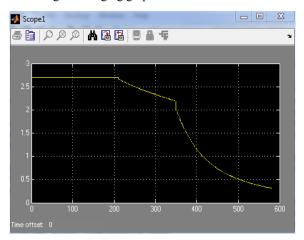

Fig. 5 : 27 level Asymmetrical Multi Level Inverter Output\_ for ACMLI

#### V. SIMULATION RESULT AND DISCUSSION:

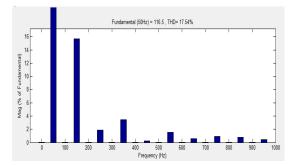

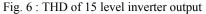

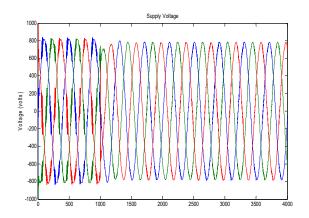

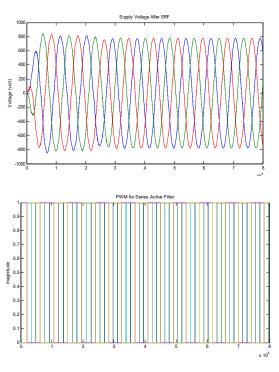

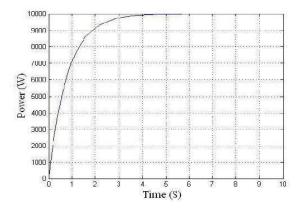

Results of simulations are shown in Fig.4.and Fig.5 and corresponding THD is shown in Fig.6 and Fig.7.

Fig. 7 : THD of 27 level inverter output

Having shown the simulation result of the 15 level and 27 level for Symmetrical step control it is observed that the Total harmonic distortion is more, hence the losses are also more in the system. But, it is the simplest method among all the methods and easy to implement in the hardware. More methods with less THD would be described in the next paper.

| ACMLI   | NO.OF<br>BRIDGES | NO.<br>VOLTAGE<br>LEVELS | THD<br>(%) |

|---------|------------------|--------------------------|------------|

| DDIADX  | 2                | 7                        | 25.47      |

| BINARY  | 3                | 15                       | 17.54      |

|         | 2                | 9                        | 22.05      |

| TERNARY | 3                | 27                       | 14.96      |

|         | 4                | 81                       | 12.90      |

TABLE III

Above result inspires us to increase the GP ratio and the no. of bridges but it has been avoided due to following limitations.

For the same no. of bridges in ACMLI ternary GP ratio has more levels then binary GP ratio, but increasing GP ratio above ternary will not increase the voltage levels.

By using four bridges and ternary voltage ratio we can have the 81 level output voltage, but more bridges increase the cost and hence their losses, and will reduce the efficiency. Further for fourth bridge DC source is 27 times the DC source voltage for the first bridge and hence bridge requires much more different power rating still have to carry the same current. Rating of the fourth bridge would be 27 times higher than rating of the first bridge and for 81 level inverter switching losses are also increased. When we use the 3 bridges THD is 14.96 with additional one bridge it reduces to 12.9 that is not a great reduction. Hence, In ACMLI use of ternary GP ratio with three bridges that is 27 level is optimum.

#### **VI. CONCLUSION**

The scheme of Symmetrical step control technique for ACMLI was proposed to improve the output voltage of CMLI. And it has been conclude that by increasing no. of levels for the output voltage, the THD can be reduced. No. of levels can be increased by increasing the no. of bridges of MLI, Further for same no. of bridges in ACMLI, in ternary voltage progression has more voltage levels then binary and 3-bridge 27 level is an optimum value of Multi level inverter. Other methods with less THD would be considered for the future work.

#### REFERENCES

- J. S. Lai and F. Z. Pen& 'Multilevel converters -A new breed of power umverters", EEE Tram. Zd. &I., v. 32, pp. 509-5 17, May/June 1996.

- [2] B. S. Suh, G. Sinha, M. D. Manjrekar, T. A. Lipo, "Multilevel Power Conversion – An Overview of Topologies and Modulation Strategies", IEEEOPTIM Conference Record, pp. 11-24, vol. 2, 1998

- [3] M. D. Manjrekar, P. K. Steimer, and T. A. Lipo, "Hybrid multilevel power conversion system: a competitive solution for high-power applications," Industry Applications, IEEE Transactions on, vol. 36, pp. 834-841, 2000.

- [4] J. S. Manguelle, S. Mariethoz, M. Veenstra and A. Rufer, "A generalized design principle of a Symmetrical step asymmetrical multilevel converter for high power convasion," in EPERec., 2001, CD-ROM

- [5] Kuhn, H. Ruger, N.E. Mertens, A., "Control Strategy for Multilevel Inverter with Non-ideal DC Sources", Power Electronics Specialists Conference (PESC), Hanover, 2007.

- [6] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. Perez, "ASurvey on Cascaded Multilevel Inverters," Industrial Electronics, IEEE Transactions on, 2010.

### **Multi-Resonating UWB Printed Monopole Antenna**

#### K. P. Ray & S. S. Thakur

SAMEER, IIT Campus, Powai, Mumbai-400076, India

*Abstract* - Ultra wideband printed monopole antenna with multi resonating patches has been presented. The proposed antenna is designed to operate from 1.3 GHz to cover the range up to 12 GHz, which is well beyond defined ultra wideband range of 3.1 GHz to 10.6 GHz. The theoretical results have been verified with experiments with reasonably good agreement.

Keywords - Multi resonating antenna; open ended resonator; ultra wide bandwidth (UWB; printed monopole antenna.

#### I. INTRODUCTION

With exponential rise of wireless communication applications, and the approval of ultra wideband (UWB) for public use by the FCC in February 2002 [1], the requirement of multi-band UWB antenna has increased. Earlier, designs of single patch of square, rectangular, circular and elliptical shape printed antennae have been reported. The current distribution on these antennae is on the edges of the patch, thus antenna performance is not strongly dependent on central part of the patch. Previously, multi resonating antennae with multiple elements have been reported [2-3]. In these antennae, either size is increased or they do not fully cover the impedance bandwidth for lower end of UWB range.

The combination of two or more resonating elements will generate overlapping multiple resonances, resulting in multiband antenna or UWB antenna. When more resonating elements are present then it becomes difficult to get impedance matching for entire UWB therefore optimization is needed for feed, i.e. feed length, feed position, coupling of feed to the driver resonator and coupling between the resonators. These things have been considered for the proposed antenna to obtain UWB response. The proposed antenna in this paper has lesser effective area and hence small antenna size would be an important parameter for selection in portable communication systems [4-5]. In this paper, multi-resonator has been presented, which yields the bandwidth over 10.7 GHz centered around 6 GHz, from 1.3 GHz to 12 GHz. This range would be very useful for 1800GSM, 1900PCS, 2.4GHz Bluetooth - ISM, AWS, UWB and Radio Relay System beyond 11 GHz [4-6].

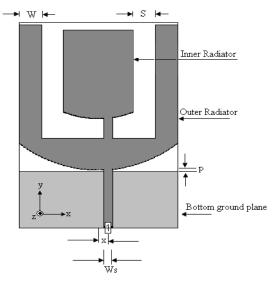

#### **II. GEOMETRY AND DESIGN OF ANTENNA**

A. Resonance frequencies

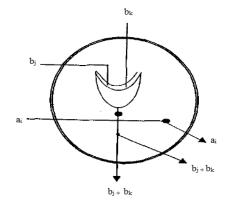

The antenna configuration is shown in Fig. 1. The multi resonating structure will have two resonances for two different elements. The outer structure is open ended resonator and will have lower edge frequency instead of resonance frequency. The  $f_L$  is approximated as given in (1) [7].

$$f_{\rm L} = c/\lambda_{\rm L} \tag{1}$$

where,  $\lambda_{\rm L} = 2 {\rm L} \left[ \sqrt{(\varepsilon_r + 1)/2} \right]$ ,  $\varepsilon_r$  is the dielectric constant of the FR4 substrate, which for the present case is 4.3 and the L can be measured with the help of longest current path in outer structure.

#### B. Geometry

The configuration is shown in fig. 1. The multiresonating printed monopole antenna is basically using a rectangular patch of size 50 mm x 40 mm, which is designed at lower band-edge frequency of around 1.30 GHz by using equation (1) [7]. A rectangular patch of 36 mm x 37 mm has been chopped off to leave width W= 7 mm. To reduce the lower band-edge frequency, f<sub>L</sub>, the outer structure length has been increased by 2 mm; this makes it U-fork type structure. To improve matching from source to radiator the bottom of the patch is made circular with the arc of radius = 38 mm and centre for the arc is decided by adjusting feed length of p=0.2 mm.

Second rectangular structure of size 22 mm x 29 mm is designed with the spacing S = 7 mm between two resonators. For improving of matching at the input of the second radiator, circular bottom of arc radius of 27 mm centre is optimized. The vertical gap between two radiating patches is 6.775 mm. The multi-resonating printed monopole antenna configuration is fabricated on FR4 substrate of size 50 mm x 72 mm, thickness =1.59

mm, dielectric constant,  $\varepsilon_r = 4.3$  and loss tangent  $\tan \delta = 0.01$ .

Fig. 1: Geometry of Multi-Resonating Printed Monopole Antenna

A microstrip line feed with partial backing ground plane of size 50 mm x 20 mm has been used [5], [8]. The microstrip feed line is designed with width of Ws = 2.8 mm for the impedance of 50  $\Omega$ . The feed position is optimized so that two resonators are excited with good input match, leading to larger bandwidth. The 50  $\Omega$  feed position has been chosen by moving the microstrip feed along the base (horizontally along the x-axis) of the configuration to obtain improved input match at x = 3 mm with feed length of p= 0.2 mm, as shown in Fig. 1 matching over large bandwidth is obtained [9]. The theoretical analysis of this configuration has been carried out using IE3D software [10].

#### **III. RESULTS**

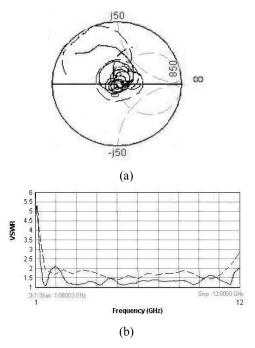

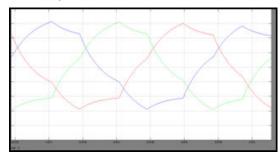

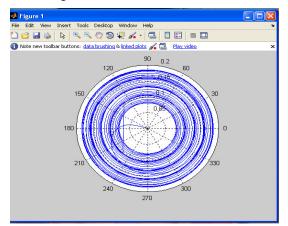

The theoretical results have been validated by experiment. The input impedance, bandwidth corresponding to VSWR  $\leq 2$ , radiation patterns etc of this antenna have been measured. The simulated and measured input impedance loci and corresponding VSWR, are shown in Fig. 2 (a) and (b), respectively. It has been observed that the measured bandwidth for VSWR  $\leq 2$  is from 1.3 GHz to 12 GHz (BW = 10.7 GHz) while the corresponding simulated bandwidth is from 1.4 GHz to 11.4 GHz (BW = 10 GHz).

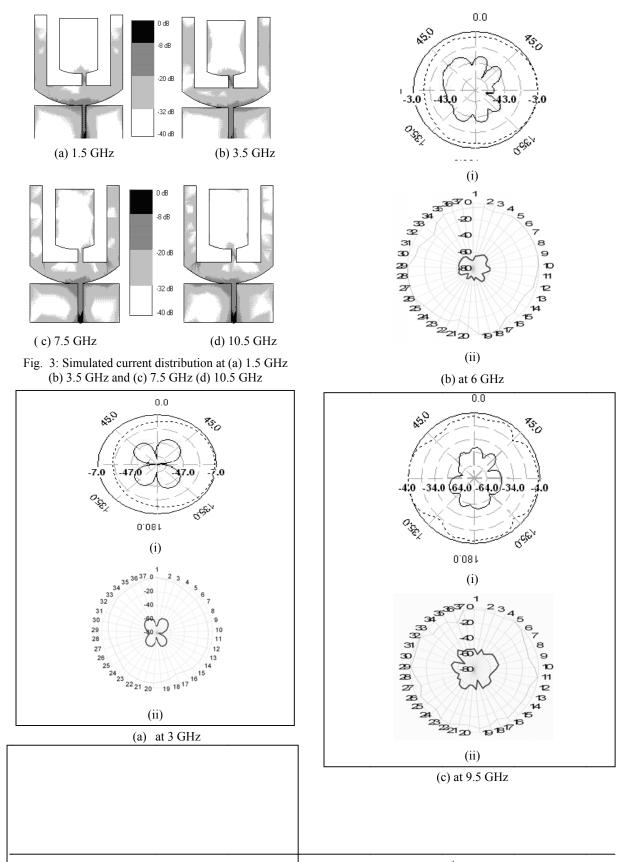

For the insight simulated current distributions of the proposed multi-resonator antenna are presented in Fig. 3. The current distribution shows the existence of resonant mode and their harmonics at higher order modes. Current distribution at 1.5 GHz shows that the

outer U-fork resonates at own frequency, where as inner patch does not get excited. At 3.5 GHz inner patch resonates and outer patch gives harmonics. Similarly at 7.5 GHz and 10.5 GHz both the resonators yield higher order harmonics.

The radiation patterns were simulated over the complete impedance bandwidth and experiments were conducted to validate the same which are shown for three frequencies at 3 GHz, 6 GHz and 9 GHz. The azimuthal radiation pattern is similar to omni directional. At higher frequency, radiation patterns are similar to that of at lower frequency with more variations in radiation patterns. Fig. 4 shows the simulated and measured azumuthal radiation patterns with reasonable agreement. The differences between the measured and simulated radiation patterns are due to manual alignment errors and reflections from the various objects present inside the laboratory, where measurements were carried out.

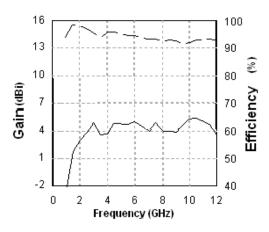

Fig.5 shows the plots of maximum gain and radiation efficiency. The gain varies between 4 dBi to 5 dBi in the complete bandwidth and the corresponding variation in the radiation efficiency is between 98% and 92%, which makes the antenna a very efficient radiator in the required frequency range.

Fig. 2 : Theoretical and measured (a) Impedance Loci and (b) VSWR  $% \left( {{{\bf{F}}_{{\rm{A}}}} \right)$

(-----Simulated, \_\_\_\_ Experimental)

International Conference on Electrical, Electronics & Computer Engineering (ICEECE)- 11th February, 2012 - Ahmedabad

International Conference on Electrical, Electronics & Computer Engineering (ICEECE)- 11th February, 2012 - Ahmedabad

Fig. 4 : Simulated and measured azumuthal radiation patterns at (a) 3 GHz (b) 6 GHz and (c) 9.5 GHz (i) Simulated, (ii) Experimental (-----Co-pol, \_\_\_\_\_ Crosspol)

Fig. 5 : Maximum gain and radiation efficiency versus frequency (GHz) (----efficiency, \_\_\_\_\_ gain)

Fig. 6: Photograph of the fabricated Multi-Resonating Printed Monopole Antenna

Fig. 6 shows the photograph of the fabricated antenna of optimized configuration.

#### **IV. CONCLUSION**

A very simple design of multi-resonating UWB antenna has been proposed. The proposed printed monopole antenna has radiation pattern similar to the conventional dipole antenna. The antenna yields ultra wide bandwidth. The measured and simulated bandwidth ratio of this antenna is 10.7:1 and 10:1, respectively for VSWR  $\leq 2:1$ , which is very useful range for many communication bands.

#### REFERENCES

- Revision of Part 15 of the Commission's Rules Regarding Ultra-Wideband Transmission Systems, ET Docket 98-153, Federal Communications Commission, FCC 02-48, First Report And Order, Adopted: February 14, 2002 Released: April 22, 2002.

- [2] K. Rambabu, M. Alam, J. Bornemann and M. A. Stuchly, "Compact wideband dual-polarized microstrip patch antenna", IEEE Antenna and Propagation Society International Symposium, Vol. 2, pp 1955-1958, June 2004.

- [3] K. Rambabu, H. A. Thiart, J. Bornemann and S. Y. Yu, "Ultrawideband printed-circuit antenna", IEEE Transactions on Antenna and Propagation, Vol. 54, pp 3908-3911, December 2006.

- [4] M. Nabil Srifi, M. Aznabet, O. El Mrabet, N. Aknin, and M. Essaaidi, "UWB Compact monopole antennas for breast cancer detection", Le 19EME Colloque International, Valence – France, September 2007.

- [5] K. P. Ray, "Design aspect of printed monopole antenna for ultra-wide band applications", Article ID 713858, Hindawi Publishing Corporations, International Journal of Antennas and Propagations, Vol. 2008.

- [6] Rec. ITU-R F.387-6, Radio-frequency channel arrangements for radio relay systems operating in the 11 GHz band, 1992-03.

- [7] Zhi Ning Chen, Terence S. P. See, and Xianming Qing, "Small printed ultrawideband antenna with reduced ground plane effect", IEEE Transactions on Antenna and Propagation, Vol. 55, pp 383-388, Feb 2007.

- [8] K. P. Ray and Y. Ranga, "Printed rectangular monopole antennas", IEEE Antennas and Propagation Society International Symposium, Vol. 9, pp 1693-1696, 2006.

- [9] Girish Kumar and K. P. Ray, "Broadband microstrip antennas", Artech House, Boston, 2003.

- [10] Zeland Software Inc., IE3D ver. 12, 2007.

#### **\* \***

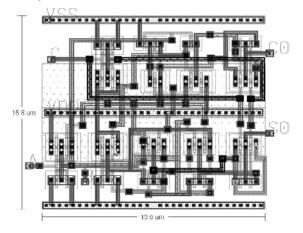

## Performance Evaluation of Multiplier - Architecture Based on Switching Activity Minimization

#### Beena Thomas, S. Arul Mozhi & Sudarmani.R

ECE Department, Faculty of Engineering, Avinashilingam Deemed University for Women, Coimbatore, Tamil Nadu, India

Abstract - Multipliers are the fundamental components of many digital systems. It has wide range of applications in digital signal processing, wireless sensor networks and portable digital systems and hence their power and area are of prime concern. Power management has become a great concern in VLSI design in recent years. Power consumption in conventional multiplier mainly depends on switching activities and hence leads to more power dissipation. In this paper modifications are done in shift and add architecture of multiplier by removal of shifting in B register, direct feeding of A to the adder, bypassing the adder whenever possible, using a ring counter instead of a binary counter and removal of the partial product shift for minimizing the switching activity, thereby reducing the power consumption and area occupied. The simulation results shows that shift and add architecture occupies only 50% of area and saves power five times compared to conventional multiplier.

Keywords - Low-power multiplier, Low-power ring counter, Shift-and-Add multiplier, switching activity reduction.

#### I. INTRODUCTION

Research in VLSI towards reduction in area, power, cost and increase in performance and reliability of the circuit. However, this has begun to change and, increasingly, power is being given comparable weight to area and speed considerations. The wireless communications systems such as personal digital assistants, personal communicators, portable desktops, audio- and video-based multimedia products needs highspeed computation and low power consumption. To save significant power consumption of a VLSI design, it is a good direction to reduce its dynamic power that is the major part of total power dissipation.

The power consumption in digital CMOS circuit can be described by the following expression:

#### $P_{avg} = P_{Dynamic} + P_{Shortcircuit} + P_{Leakage} + P_{Static}$

The dynamic power dissipation is caused by charging and discharging of capacitances in the circuit. The short circuit power consumption is caused by the current flow through the direct path existing between the power supply and the ground during the transition phase. The n-MOS and p-MOS transistors used in a CMOS logic circuit commonly have non zero reverse leakage and sub threshold current. Multipliers are fundamental components of digital hardware. They occupy a relatively large portion of the overall chip area and have often been the limiting factor in terms of speed. The computation of a multiplier manipulates two input data to generate many partial products for subsequent addition operations, which in the CMOS circuit design require many switching activities. Switching activity of a circuit can be expressed as the summation over all operation types performed, as the product of operation frequency and the number of transitions per operation. The switching activities within the functional unit of a multiplier accounts for the majority of the power dissipation of a multiplier, as given in the following equation:

#### $P_{\text{Switching}} = \alpha c v_{\text{dd}}^2 f_{\text{clk}}$

Where  $\alpha$  is the switching activity parameter, c is the loading capacitance,  $v_{dd}$  is the operating voltage and  $f_{clk}$  is the operating frequency. Minimizing the switching activities can effectively lower power dissipation without affecting the circuit operation performance.

The generation of partial product and shifts in registers leads to more consumption of power and area. Among multipliers, the carry-select-adder based radix multipliers, which have lower area overhead, employ a greater number of active transistors for the multiplication operation and hence consume more power. The tree multipliers are used in high speed applications such as filters, but these require large area. Higher-radix multipliers are faster but consume more power since they employ wider registers, and require more silicon area due to their more complex logic. Among other multipliers, shift-and-add multipliers have been used in many other applications for their simplicity and relatively small area requirement [1]-[3]. In this paper, the shift and add architecture is designed and it has more power advantage compared to other multipliers.

This paper is organized as follows: Section II briefly reviews the background information about conventional shift and adds multiplier. Section III describes the architecture description of the low power multiplier. Section IV describes the low power ring counter architecture. Results are discussed in section V and conclusion is in the last section.

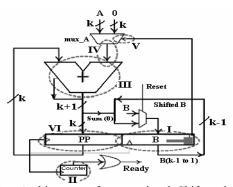

#### II. SHIFT AND ADD MULTIPLIER

The architecture of a conventional shift-and-add multiplier, which multiplies A by B, is shown in Figure 1. The dashed ovals show the major sources of switching activities. The multiplier is shifted in each cycle and the bit which getting out of register B is connected to the select pin of multiplexer, mux A. As the select signal changes, the output of mux A also changes. This causes the adder operation. The partial product is required to be shifted in every cycle. The counter is for checking whether the required number of operations has been performed. The six major sources of switching activity are: (a) Shifting of the 'B' register. (b) Activity in the counter. (c) Activity in the adder. (d) Switching between '0' and 'A' in the multiplexer. (e) Activity in the multiplexer select. (f) Shifting of the partial product register. By eliminating or reducing the switching activity described above, low power architecture can be derived.

Fig. 1 : Architecture of conventional Shift and Add multiplier with major source of switching activity

#### A. B REGISTER:

To generate the partial product, B (n) is used to decide between A and 0. If the bit is "1", A should be added to the previous partial product, whereas if it is "0", no addition operation is needed to generate the partial product. Hence, in each cycle, register should be shifted to the right so that its right bit appears at B (n) this operation gives rise to some switching activity.

#### B. ADDER:

In each cycle, the current partial product is added to A (when B (n) is 1) or to 0 (when B (n) is 0). This leads to unnecessary transitions in the adder when B (n) is zero.

#### C. PARTIAL PRODUCT REGISTER:

In each cycle, the current partial product is added to A (when B (n) is 1) or to 0 (when B (n) is 0). This leads to unnecessary transitions in the adder when B (n) is 0; the partial product is shifted in each cycle giving rise to transitions. The multiplication algorithm reveals that multiplication may be completed by processing the most significant bits of the partial product and hence, it is not necessary for the least significant bits of the partial product to be shifted. The data transparency problem of latches prohibits us from using latches instead of flip-flops for forming the lower half of the partial product.

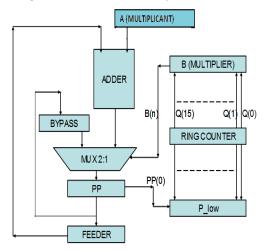

#### **III. LOW POWER MULTIPLIER**

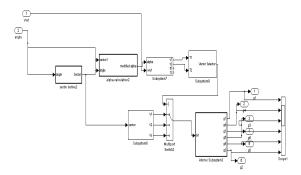

The architecture of a low power multiplier is shown in Figure 2. The major modifications made are the removal of the multiplier shifting, direct feeding of multiplicand to the adder, Reduction in partial product shifting, bypassing the adder whenever possible and use of a ring counter instead of a binary counter.

Fig. 2 : Architecture of Low Power Multiplier

#### A. SHIFTS OF B-REGISTER

To generate partial product in conventional architecture B (0) is used to decide between A and 0. In each cycle, register B should be shifted to right giving rise to more switching activity. The shift and add multiplier is proposed where the multiplexer with one hot encoded bus selector chooses the hot bit of B in each cycle. A Ring counter is used to select B (n) in nth cycle thereby reducing the switching activity.

#### B. ACTIVITY OF ADDER

There is an unnecessary transition in adder when B (n) is 0 in conventional multiplier. In such cases, the adder can be bypassed and the partial product should be shifted to right by one bit. So, in Shift and Add Multiplier the feeder and bypass registers are used to bypass the adder in the cycles when B (n) is 0. In each cycle, the hot bit of the next cycle is checked. If it is 0, the adder is not needed in the next cycle; the bypass register is clocked to store the current partial product. If it is 1, the adder is really needed in the next cycle; the feeder register is clocked to store the current partial product which must be fed to the adder in the next cycle. To select between the feeder and the bypass registers NAND and NOR gates of inverting logic is used. When the hot bit B (n) is 0, there is no transition in the adder. This enables to remove the multiplexer and feed input A directly to the adder, reducing in a noticeable power saving.

#### C. SHIFTS OF PARTIAL PRODUCT REGISTER

In the conventional architecture, the partial product is shifted in each cycle giving rise to transitions. The multiplication algorithm reveals that the multiplication may be completed by processing the most significant bits of the partial product. It is not necessary for the least significant bits of the partial product to be shifted. In the Shift and Add architecture, for lower half of partial product we use latches. So, the least significant bit (LSB) of PP (0) is stored in right most latch of PP register. The ring counter output is used to open the proper latch when he last bit is stored in the left most latch, the higher and lower halves of the PP form the final product result.

Power is saved by two reasons,

- 1) Lower half of the PP is not shifted.

- 2) This half is implemented with latches instead of Flip flops.

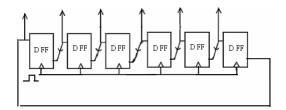

#### **IV. RING COUNTER**

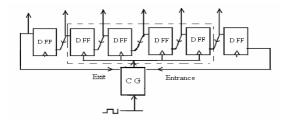

The counter used in the conventional multiplier has large number of switching activities. An n bit synchronous ring counter is built by cascading n flip flops in a chain. The conventional Ring Counter is shown in the figure 3.

Fig. 3 : Conventional synchronous ring counter

All flip flops have a common clock signal and each clock pulse is applied to all flip flops whereas the movement of '1' in the counter chain reveals that each clock pulse must be applied to only two flip flops. So, in each clock pulse  $(n-2) \times s$  unnecessary transitions are raised where, 's' is the total number of transitions raised in single flip flop, 'n' is the number of flip flops.

#### A. SHIFTING OF THE MULTIPLIER USING RING COUNTER

An example of a shift and add Multiplication is

| $A \rightarrow$ | 011                | Х   |            |   |

|-----------------|--------------------|-----|------------|---|

| В→              | 010                | =   |            |   |

|                 |                    |     |            |   |

|                 | 000                |     | (B(0) = 0) | ) |

|                 | 011                |     | (B(1) = 1) | ) |

| 0               | 0 0                |     | (B(2) = 0) | ) |

|                 |                    |     |            |   |

| An              | swer $\rightarrow$ | 001 | 10         |   |

#### Fig. 4 : Shift and Add Multiplication

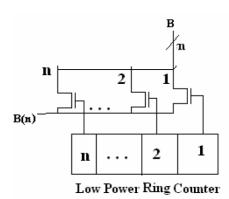

In each step for generating the partial product, the corresponding bit of the multiplier is needed; it is shown as B (0), B (1) and B (2) in figure 4. For getting the corresponding multiplier bit, the multiplier is required to be shifted. If the required bit is obtained without shifting, considerable power saving can be achieved. This is achieved by using a ring counter as shown in Figure 5.

#### B. LOW POWER RING COUNTER

The ring counter used in the shift and add multiplier is noticeably wider than the binary counter used in the conventional architecture. To minimize the switching activity of the counter we use low power ring counter.To reduce the switching activities only some flip flops can be clock gated. A flip flop in a ring counter must be clocked if and only if either its input or output is '1' immediately before the triggering clock edge comes. So only two flip flops must be clocked in each cycle.

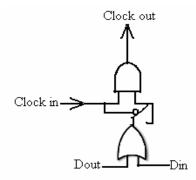

Fig. 5 : Low Power Ring Counter

The clock gating logic with flip-flops' input and output is shown in the figure 6,OR's the value of flip flop's input and output on Positive clock edges stores the result in latch. The output of the latch determines whether or not to gate the clock signal .This clock gator is positive edge triggered.

Fig. 6 : Clock Gating Structure

To avoid all the unnecessary transitions raised by the clock signal each flip-flop should be provided with the clock gating circuitry of above figure 6, but this solution ends up with a large area overhead plus due to transitions in clock gator themselves the resulting ring counter will not have fewer switching activity. A better solution is used in the low power multiplier architecture.

Fig. 7 : Low Power Architecture for Ring Counter with Block of Size 4

One of the important properties of the ring counter is that its output is one hot encoded. This property of the ring counter makes its output wide especially as the counter size increases. To reduce the switching activity of the counter the counter is partitioned in to a number of blocks which are clock gated with a special clock gating structure whose power and area overheads are independent of the block size, controlling with the low power ring counter helps to get a low power low area architecture, thus avoids the trade off between power and area [5], [8], [9]. The clock gating structure is shown below Fig 8.

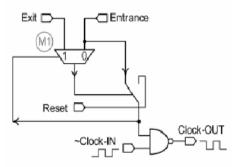

Fig. 8 : Clock Gating Structure for the Low Power Ring Counter

The clock gating structure for hot block ring counter is composed of a multiplexer, a NAND gate, and a resettable latch. In addition to the reset and clock IN signals, there are two other signals called Entrance and Exit, coming from the neighboring left and right blocks. These are used to determine whether the '1' is present in the block to which the output of the Clock gating goes.

#### V. RESULTS AND DISCUSSIONS

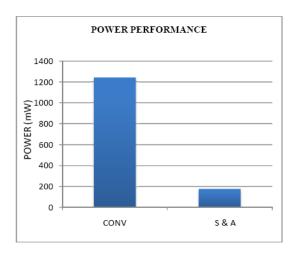

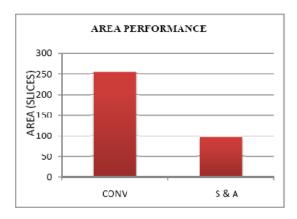

Low Power Shift and Add Multiplier of 8 bit is verified using MODELSIM10.0a with VERILOG code. The comparison of multipliers in terms of Power and Area is shown in Table 1.

| PARAMETERS    | CONVENTIONAL<br>MULTIPLIER | SHIFT AND<br>ADD<br>MULTIPLIER |

|---------------|----------------------------|--------------------------------|

| POWER<br>(mW) | 1244                       | 253.65                         |

| AREA (slices) | 180                        | 96                             |

The graphical representation of multipliers in terms of Power and Area is shown in figure 9 and figure 10.

Fig. 9 : Comparison between Conventional Multiplier with Low Power Multiplier in terms of Power

Fig. 10 : Comparison between Conventional Multiplier with Low Power Multiplier in terms of Area

When compared to conventional multiplier, the shift and add architecture occupies 50% of area and hence area minimization occurs. Also power consumption is five times lower than conventional multiplier.

#### VI. CONCLUSION

The multiplier is explored based on shift and add architecture. The multiplier system is suitable mainly for portable digital systems, microelectronic devices, DSP's. The modifications to the conventional architecture included the removal of the shift of the B register, direct feeding of A to the adder, bypassing the adder whenever possible, use of a low power ring counter instead of the binary counter, and removal of the partial product shift. Low-power architecture for ring counter is proposed based on partitioning the counter into blocks of flip-flops clock gated with a special clock gating structure and the complexity of which was independent of the block sizes. The simulation results prove that shift and add multiplier performance is better than conventional multiplier. Therefore, this multiplier is feasible for any low power low area applications.

#### REFERENCES

- A.Chandrakasan, T.Sheng, R.W.Brodersen, "Low Power CMOS Digital Design," Journal of Solid State Circuits, No.27, PP.473–484, April 1992.

- [2] N.Y.Shen and O.T.C. Chen, "Low power multipliers by minimizing Switching activities of partial products," in Proc. IEEE Int.Symp.Circuits Syst., May 2002, Vol.4, PP. 93-96.

- [3] O.T.Chen, S.Wang and Y, W.Wu, "Minimization of switching activities of partial products for designing low power multipliers," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., Vol. 11, No. 3, PP. 418–433, Jun. 2003.

- [4] Hen and Y.S.Chu, "A low power multiplier with spurious Power suppression technique," IEEE Trans. Very Large Scale Integer (VLSI) Syst., Vol.15, No-7, PP. 846-850, July 2007.

- [5] Ercegovac M.D. and Huang Z, "High performance low power left to right array multiplier design," IEEE Trans. Comput., Vol-54, No-2, PP. 272-283, March 2006.

- [6] J.S.Wang, C.N.Kuo, T.H.Yang, "Low-power fixed-width array multipliers," IEEE Symp.Low Power Electron. Des, 2004, pp. 307–312.

- [7] K.H.Chen, Y. M. Chen, Y. S. Chu, "A versatile multimedia functional unit design using the spurious power suppression technique," in Proc.IEEE Asian Solid-State Circuits Conf., 2006, pp. 111–114.

- [8] K. H. Chen, K. C. Chao, J. I. Guo, J. S. Wang, and Y. S. Chu, "An efficient Spurious Power Suppression Technique (SPST) and its applications on MPEG-4 AVC/H.264 transform coding design," in Proc. IEEE Int. Symp. Low Power Electron.Des, 2005, PP. 155–160.

- [9] V.P.Nelson, H.T.Nagle, B.D.Carroll, J.I.David, "Digital logic Circuits analysis and design," PH Hall, 1996.

- [10] Jinn-Shyan Wang, Shiang-Jiun Lin, Chingwei Yeh, "A Low-Power High-SFDR CMOS Direct Digital Frequency Synthesizer," in Proc. IEEE 2005.

- [11] Ming-Chen Wen, Sying-Jyan Wang, and Yen-Nan Lin, "Low Power Parallel Multiplier with Column Bypassing," in Proc. IEEE 2005.

- [12] C. S. Wallace, "A Suggestion for a Fast Multiplier," IEEE Transactions on Electronic Computers, Vol. EC- 13, PP. 14-17, Feb.1964.

- [13] L. Dadda, "On Parallel Digital Multiplier," Alta Frequency, No. 45, PP. 574-580, 1976..

- [14] Chi-Ming Tsai, Tsai-Min Chiang, Chyi-Hui Hong, Kun-Tien Kuo, Rung-Bin Lin, "A Low Power-delay-product Multiplier with Dynamic Operand Exchange," in Proc. IEEE 2000, pp. 501 -504

- [15] Zhan yu, Larry Wassermann and Alan n. willson, "A painless way to reduce power dissipation by over 18% in booth-encoded carry- save array multipliers for Dsp," in proc. IEEE 2000.

**~~**

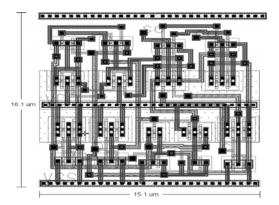

## Efficient Bit-Parallel Systolic Multiplier for Special Class of GF (2<sup>m</sup>)

B. Sargunam<sup>1</sup>, S. Arul Mozhi<sup>2</sup> & R. Dhanasekaran<sup>3</sup>

<sup>1&2</sup>Department of ECE, Faculty of Engineering, Avinashilingam University for Women, Coimbatore, India <sup>3</sup>Syed Ammal Engineering College, Ramanathapuram, India

Abstract - A bit parallel systolic multiplier in the finite field  $GF(2^m)$  over the polynomial basis where irreducible polynomial, all one polynomial (AOP) and an irreducible trinomials generate the field  $GF(2^m)$  is presented. The complexity of the multiplier is compared in terms of area, latency and power. The AOP based multiplier and the multiplier with irreducible trinomial has high throughput as compared with the traditional systolic multipliers. Moreover, these multipliers are highly regular, modular, and therefore, well-suited for VLSI implementation.

Keywords - Galois Field, cryptography, Bit parallel systolic multiplier, AOP.

#### I. INTRODUCTION

Finite fields of the form  $GF(2^m)$  have found applications in the implementation of error-correcting codes such as Reed-Solomon (RS) codes and also certain cryptographic systems [1-3]. Addition and multiplication are two basic arithmetic operations in finite fields. Addition operation is easily realized using XOR gates but the multiplication operation is costly in terms of component counts and time delays [4]. Finite field multiplication is the most important arithmetic operation because it is nontrivial to implement in hardware and frequently required in both the encoding and decoding algorithm of cryptography. The other operations such as division and exponentiation can be performed by repeated multiplication. This study focuses on the hardware implementation of fast and low-complexity multipliers over GF(2<sup>m</sup>) since computing exponentiation, division, and computing multiplicative inverse can be performed by computing multiplication iteratively. Many bit parallel systolic multipliers have been proposed in [5-7], the fields in these multipliers are defined by irreducible polynomial. However, they are inefficient for cryptographic applications due to the system's complexity. In this paper, general polynomial, irreducible trinomial systolic multiplier over GF(2<sup>m</sup>) and AOP based simple bit parallel systolic architecture, using redundant basis are compared. The first multiplier is composed of m<sup>2</sup> identical cells. Each cell consisting of two 2-input AND gate and two 2-input XOR gate. The second multiplier circuit includes m<sup>2</sup> 'U' cells and

(m-1) 'V' cells, in which the 'U' cell is composed of one 2- input AND gate, one 2- input XOR gate and 'V' cell consists of one 2- input XOR gate. The third one is composed of  $(m+1)^2$  identical cells, each consisting of one 2-input AND gate and one 2-input XOR gate. The latency of the systolic multiplier using irreducible trinomial is only (2m-1) clock cycles with a throughput rate of one result per clock cycle. The clock period is given by the propagation delay of a signal through a 2input AND gate and 2- input XOR gate.

#### **II. PRELIMINARIES**

Galois field (GF) is a popular name for a field with finite number of elements. The simplest example of a GF is the binary field which consist of elements  $\{0, 1\}$ and referred to as GF(2). We can create larger fields by extending GF(2) into vector space leading to finite fields of size 2<sup>m</sup>. These are simple extensions of the base field GF(2) over 'm' dimensions. Field element can be derived by two alternate representations. In the first representation, all elements of GF(2<sup>m</sup>) may be represented as powers of a primitive field element  $\alpha[2]$ , for example if m=8,then the field element is of the form  $\alpha^n$  for n=0,1,....255. In the second representation, each element has an equivalent representation as a binary mbit. A polynomial of the form  $P(x) = (p_0 + p_1 x +$  $p_2x^2 + \dots + p_mx^m$ ) over GF (2) is called an all in one polynomial of degree 'm'. For an irreducible polynomial of degree 'm', the polynomial P(x) is formed as  $x^m$  $+ x^{n} + 1$  with m > n > 0 is known as a trinomial polynomial.

International Conference on Electrical, Electronics & Computer Engineering (ICEECE)- 11th February, 2012 - Ahmedabad

Galois field includes three different basis namely polynomial (standard), normal and dual basis. The polynomial basis of GF(2<sup>m</sup>) can be expressed in the form  $\{1, \alpha, \alpha^2, \dots, \alpha^{m-1}\}$ , where ' $\alpha$ '  $\in GF(2^m)$  be the root of a primitive polynomial of degree 'm' over GF(2). The primitive polynomial p(x) can be written as (1 + $x^{2}+x^{3}$ ) for the finite field over GF(2<sup>3</sup>). When using a polynomial basis representation, any element of the field  $GF(2^m)$  can be expressed as a binary polynomial of degree at most (m-1). The standard alternative basis for polynomial basis is a normal basis which is represented in the form { $\alpha$ ,  $\alpha^2$ ,  $\alpha^4$ ,....,  $\alpha^{(2)^m-1}$  } where ' $\alpha$ ' is the root of an primitive polynomial of degree 'm' over GF(2). A dual basis is not a concrete basis like the polynomial basis and the normal basis rather it provides a way of using a second basis for computations. Consider two bases for elements in a finite field  $GF(2^m)$  such that  $B_{1} = \{ \alpha_{0}, \alpha_{1}, \alpha_{2}, \dots, \alpha_{m-1} \}$  and  $B_{2} = \{ \gamma_{0}, \gamma_{1}, \gamma_{2}, \dots, \gamma_{m-1} \}$  then  $B_{2}$ can be considered a dual basis of  $B_1$  provided that Tr  $(\alpha_i, \gamma_i) = \{0, if i \neq i \text{ and } 1, otherwise. 'Tr'$ denotes the trace function in dual basis. This basis provides a way to easily communicate between devices that use different bases, rather converting explicitly between the bases using the change of bases formula.

Normal basis representation offers the best performance in hardware [8-10] and polynomial basis representation is more efficient in software. Using the normal basis representation, the squaring of an element in GF(2<sup>m</sup>) is readily shown to be a simple cyclic shift of its binary digits. The main difficulties for fast normal basis multiplication in software are due to the particular computation process. First, when multiplying two elements represented in normal basis according to the standard formula, the coefficients of their product need to be computed one bit at a time. Second, the computation of a given bit involves a series of "partial sums" which need to be computed sequentially in software. To avoid the above difficulties, the normal basis multiplier realized in hardware which performs the two computations in parallel [11]. Polynomial basis multipliers are more efficient and most widely used when compared with multipliers based on normal or dual basis because polynomial basis multiplication requires a polynomial multiplication followed by a modular reduction. In practice, these two steps can be combined.

Mastrovito [12] developed a new method for multiplication where a product matrix was introduced to combine the above two steps together. The dual basis multiplier uses the dual basis representation for the multiplicand and standard basis for the multiplier. The product is again in dual basis representation and this kind of multiplier can be used in RS encoding and decoding circuits and since dual basis multiplier have particularly low hardware requirements. The multipliers

over GF(2<sup>m</sup>) may be either systolic or non systolic. In multiplier implementations, many architectures applied systolic array concept. In general, a non systolic architecture has global signals. Hence if 'm' becomes large, propagation delay also increases. But the systolic architecture does not suffer from those problem because the systolic architecture consists of replicated basic cells and each basic cell is connected with its neighbouring cells through pipelining, i.e., there are no global signals. Consequently, the systolic architecture is a better choice than the non systolic architecture for a high-speed VLSI implementation. Various architectures for non-systolic style have already been presented in [12]. The various algorithms and hardware architectures for systolic multipliers over  $GF(2^m)$  have proven their efficiencies. These techniques provide optimal design of multipliers over GF(2<sup>m</sup>) with respect to complexities, delay and Most techniques focused power. on VLSI implementation and synthesis of these multipliers because VLSI implementations of these circuits are very complicated due to complex routing, non-modularity and low testability.

#### **III. BIT PARALLEL SYSTOLIC MULTIPLIER**

#### 3.1 Multiplication with irreducible polynomial:

Let A (x) and B (x) be the two elements in  $GF(2^m)$ , P(x) be the primitive polynomial used to generate the field  $GF(2^m)$  and C (x) be the result of multiplication where C (x) =A (x) . B (x) mod P(x). Then A (x), B (x), P (x) and C (x) can be expressed as follows:

$$\begin{split} A(x) &= a_{m-1}x^{m-1} + a_{m-2}x^{m-2} + \dots + a_{1}x + a_{0} \\ B(x) &= b_{m-1}x^{m-1} + b_{m-2}x^{m-2} + \dots + b_{1}x + b_{0} \\ P(x) &= x^{m} + p_{m-1}x^{m-1} + \dots + p_{1}x + p_{0} \\ C(x) &= c_{m-1}x^{m-1} + c_{m-2}x^{m-2} + \dots + c_{1}x + c_{0} \end{split}$$

The LSB-first multiplication can be performed as follows:

$$C (x) = A (x) . B (x) \mod P (x)$$

=  $b_0 A (x) + b_1 [A (x).x \mod P (x)] + b_2 [A (x).x^2 \mod P (x)] + ..... + b_{m-1} [A (x).x^{m-1} \mod P (x)].$

In the LSB-first scheme illustrated in [7], the multiplication starts with the LSB of the multiplier B (x) and each cell in the i<sup>th</sup> step where  $(1 \le i \le m)$ , performs the following computations. Multiplication over GF(2<sup>m</sup>) is associative.

A (x)<sup>(i)</sup> = [A (x)<sup>(i-1)</sup>]. x mod P (x)

C (x)<sup>(i)</sup> = A (x)<sup>(i-1)</sup>

$$b_{i-1}$$

+C (x)<sup>(i-1)</sup>

Where  $C(x)^{(0)} = 0$  and  $A(x)^{(0)} = A(x)$

#### LSB-first multiplication algorithm

Input: P(x), A(x) and B(x)Output:  $C(x) = A(x).B(x) \mod P(x)$ Initialize:  $A(x)^{(0)} = A(x), C(x)^{(0)} = 0$ For i = 1 to m do For k = m-1 down to 0 do  $a_k^{(i)} = a_{k-1}^{(i-1)} + a_{m-1}^{(i-1)}p_k$   $c_k^{(i)} = a_k^{(i-1)}b_{i-1} + c_k^{(i-1)}$ End for End for  $C(x) = C^{(m)}(x)$

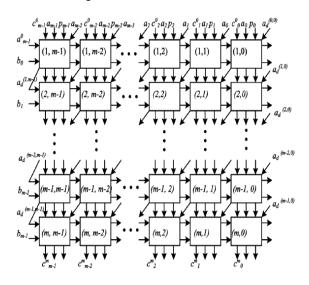

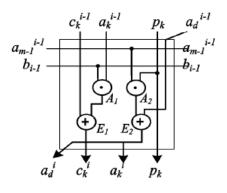

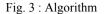

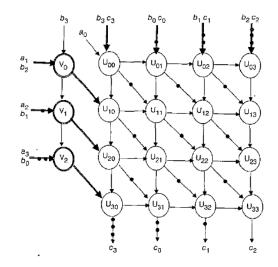

In the above algorithm  $a_k^{(i)}$  and  $c_k^{(i)}$  denote the k<sup>th</sup> coefficient in A<sup>(i)</sup> (x) and C<sup>(i)</sup> (x) respectively and b<sub>i</sub> denotes i<sup>th</sup> coefficient of B (x) and p<sub>k</sub> denotes k<sup>th</sup> coefficient of P (x). Based on the algorithm, the signal flow graph (SFG) for 'm' is drawn as shown in the figure 1 where 'm' denotes the size of the multiplier. From the SFG, it is shown that the (m x m) cells are required to implement the multiplication over GF(2<sup>m</sup>).The SFG is used for calculating the partial product and final output. The basic cell consists of two AND gates and two XOR gates. The internal architecture of the (i,k)<sup>th</sup> cell is given in figure 2. Note that in SFG, the right most cell in the first receives the input a<sub>d</sub> which is given from the output of the previous cell but there is no previous, hence the value of a<sub>d</sub> for all the cell in the right most column is zero.

Fig. 1: SFG for multiplication over  $GF(2^m)$

Fig. 2 : Circuit of (i,k)<sup>th</sup> cell

The polynomial input and polynomial output in a cell is same since it is used only for computation. Each cell computes  $a_k^{(i)}$  and  $c_k^{(i)}$  which is the coefficient A (x) <sup>(i)</sup> and C (x)<sup>(i)</sup>. The results of the basic cells in a row are given to the next row. The final result is obtained from the last row. Note that in LSB-first algorithm, the basic cell includes multiplying by x, current partial-product generation, and accumulation-to-previous-result. These operations are performed concurrently in the LSB-first scheme, but sequentially in the MSB-first scheme. This multiplier requires m<sup>2</sup> identical cells and initial delay of '3m' clock cycles.

#### 3.2 Multiplication with redundant basis:

In extended basis the multiplication of A(x) by x can be performed by shifting A cyclically once to the right [13]. That is, let A (x) =  $(a_0 + a_1x + .... + a_{m-1}x^{m-1} + a_mx^m)$  then x.A(x) =  $(a_m + a_0x + a_1x^2 + .... + a_{m-1}x^m)$ , note that  $x^{m+1} = 1$  in the extended basis. For an AOP primitive polynomial, the multiplication in extended basis can be performed as follows. Consider two elements, A and B of the extended basis. Let  $\alpha$  be a root of the irreducible AOP. Then the product P = A.B =  $(a_0 + a_1x + .... + a_{m-1}x^{m-1} + a_mx^m)$ . (b<sub>0</sub> + b<sub>1</sub>x + .... + b<sub>m-1</sub>x<sup>m-1</sup> + b<sub>m</sub>x<sup>m</sup>). The product of the multiplication can be simplified as shown below.

$$\mathbf{P} = \sum_{i=0}^{m} \sum_{j=0}^{m} \mathbf{A}_{(i-j)} \mathbf{B}_{j} \alpha^{i}$$

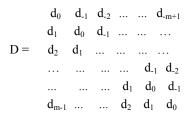

The simplified formulation and architecture for the bit parallel systolic multiplier based on the redundant basis for AOP of degree 'm' can be performed using the Toeplitz matrix manipulation. A Toeplitz matrix or diagonal-constant matrix is a matrix in which each descending diagonal from left to right is constant. For instance, the following {m x m} matrix D is a Toeplitz matrix [15]. If the  $(i,j)^{th}$  element of D is denoted by  $d_{i,j}$  then we have  $d_{i,j} = d_{i-1,j-1}$ .

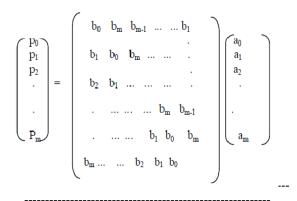

Then we can define the  $(m+1) \times (m+1)$  Toeplitz matrix and the multiplication of two elements A(x) and B(x) can be expressed in the following matrix. A systolic signal flow graph (SFG) and the internal architecture of basic cell for the AOP multiplier based on the algorithm presented in Fig 3 are given in Figure 4and 5, respectively. The elements i and j represent a row and a column of the SFG.

Input: A(x), B(x) and m.

Output:  $P(x) = A(x).B(x) \mod g(x)$ Initialize: for  $(j = 0; j \le m; j = j+1), p(0,j) = 0;$   $A = [a_m, a_{m-1}, ..., a_1, a_0], B = [b_m, b_{m-1}, ..., b_1, b_0]$ 1. for i in 1 to (m+1) do 2. for j in 0 to m do 3. p(i,j) = p(i-1,j) + a(i-1).b(j)4. end for 5. Circular right shift one bit position of B 6. end for

Fig. 4 : Systolic SFG for multiplication in GF (2<sup>m</sup>)

In general, the SFG consists of  $(m + 1) \times (m + 1)$  basic cells for multiplication over GF(2<sup>m</sup>). The basic cell in the i<sup>th</sup> row and j<sup>th</sup> column computes p(i+1, j)<sup>th</sup> internal product in (Fig. 4). The final product P(x) in vector form is given by an array of p(m + 1, j)s. To implement the SFG as a bit parallel multiplier, the outputs of the basic cells shown in fig 5 can be latched using a D flip-flop. This implementation consumes  $(m + 1)^2$  two-input

Fig. 5: Basic cell

XOR gates,  $(m + 1)^2$  two-input AND gates and  $2m^2$  D-flip-flops. The primary inputs of the SFG are assumed to be not latched. This requires 'm' clock cycles to calculate one product.

#### 3.3 Multiplication with irreducible trinomial:

This Section presents parallel systolic multiplier over the field  $GF(2^m)$  in which an irreducible trinomial of degree 'm' generates the finite field  $GF(2^m)$  discussed in [14]. For simplicity, the finite field  $GF(2^4)$  is used as an example to illustrate the architecture. Assume that  $P(x) = x^4 + x^3 + 1$  is used in the generation of the systolic multiplier. Let

A (x) =  $a_0 + a_1x + a_2x^2 + a_3x^3 B(x) = b_0 + b_1x + b_2x^2 + b_3x^3$ . The product C(x) = A(x) B(x) mod P(x) can be computed as the following iterative form:

$$T_i = T_{i-1}x + B(x) a_{m-1} \mod P(x)$$

$$T_0 = 0$$

$$T_m = C(x)$$

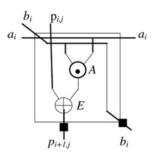

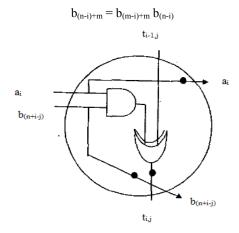

Where  $T_i = t_{0,i} + t_{1,i} + t_{2,i} + t_{3,i}$  over  $GF(2^m)$  represent the i<sup>th</sup> intermediate product of A(x) and B(x). The above computing procedure can be realised by a parallel-in parallel-out systolic array, as shown in figure 8, where 16 basic 'U' cells and 3 basic 'V' cells are used. Each U cell at position (i,j) is denoted by  $U_{i,j}$  performs the following operation, as depicted in figure 6.

$$t_{i,j} = t_{i-1,j} + a_i b_{(n+i-j)}$$

Each V cell at position  $V_i$  performes the following logic operation, as shown in figure 7.

Fig. 6 : The detailed circuit of  $U_{i,i}$  cell

Fig. 7 : The detailed circuit of V cell

Fig. 8 : Bit-parallel systolic multiplier over  $GF(2^m)$  generated by  $x^4 + x^3 + 1$

#### **IV. COMPARISON AND DISCUSSION**

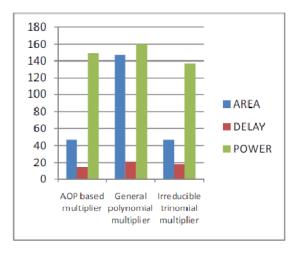

The bit parallel systolic multiplier over  $GF(2^m)$  for irreducible polynomial, trinomial and AOP have been presented. The architecture of the irreducible polynomial multiplier can also be adopted to implement AOP based multipliers and irreducible trinomial based multiplier, by reducing the complexity of basic cell and ultimately the overall system complexity can be reduced. We therefore compare the parallel multiplier of a general  $GF(2^m)$ , AOP multiplier and multiplier over irreducible trinomial.

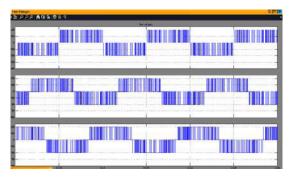

Table I reveals that the multiplier with irreducible trinomial has a smaller hardware complexity and a smaller latency than the traditional general polynomial multiplier. In addition, the trinomial multiplier has the same cell complexity. The latency of AOP based multiplier is shorter than parallel-in parallel-out systolic multiplier of GF(2<sup>m</sup>) over irreducible polynomial and trinomial. Unfortunately, irreducible AOP's are very rare. For  $m \le 100$ , the values of 'm' for which an AOP of degree 'm' is irreducible are (2, 4, 10, 12, 18,....,100). Figure 7 gives the graphical comparison in terms of area, power and delay for the general polynomial multiplier, multiplier over irreducible trinomial and AOP based multiplier. Finally, the simplicity, regularity and modularity of bit parallel systolic multiplier using irreducible trinomial over GF(2<sup>m</sup>) architecture allow for easy extension and make this design easy to implement VLSI technologies, particularly for cryptographic application.

| Multipliers                      | General<br>polynomial<br>multiplier | AOP<br>based<br>multiplier | Irreducible<br>trinomial<br>multiplier |

|----------------------------------|-------------------------------------|----------------------------|----------------------------------------|

| Items                            |                                     |                            |                                        |

| Generating polynomial            | General<br>form                     | AOP form                   | Trinomial<br>form                      |

| Array type                       | Systolic                            | Systolic                   | systolic                               |

| Number of cells                  | m <sup>2</sup>                      | $(m+1)^2$                  | U cell -<br>m^2,<br>V cell –(m-1       |

| 2-input<br>AND gate              | 2                                   | 1                          | U cell - 1,<br>V cell - 0              |

| 2-input<br>XOR gate              | 2                                   | 1                          | U cell - 1,<br>V cell - 1              |

| 1-bit latches                    | 7                                   | 3                          | 5                                      |

| Computatio<br>n time per<br>cell | $T_A + T_X$                         | $T_A + T_X$                | $T_A + T_X$                            |

| Latency                          | 3m                                  | m+1                        | 2m-1                                   |

Table I : Comparison of three systolic multiplier over  $GF(2^m)$

Fig. 9 : Comparison results of area, delay and power

#### REFERENCES

- Macwilliams F.J. and Sloane N.J.A "The theory of error correcting codes," (North – Holland, New York), 1997.

- [2] H.C.A Van Tilborg "An Introduction to Cryptography," kluwer Academic Publishers, 1998.

- [3] Peter Sweeney, "Error Control Coding from theory to practice," John Wiley & Sons, 2002.

- [4] G.B. Agnew, T. Beth, E.C. Mullin and S.A. Vanstone, "Arithmetic operations in GF (2<sup>m</sup>)," Journal cryptography, 6, 3-13, 1993.

- [5] C. L. Wang and J. L. Lin, "Systolic array implementation of multipliers for GF (2<sup>m</sup>)," IEEE Trans. Circuits . Syst., vol. 38, no. 7, pp. 796–800, Jul 1991.

- [6] M. A. Hassan and V. K. Bhargava "Bit-serial systolic divider and multiplier for finite fields GF(2<sup>m</sup>)," IEEE Transactions on Computers, 41(8):972 (980, Aug 1992.

- [7] S.K.Jain,L.Song, and K.K.Parthi, "Efficient Semi – systolic architectures for finite field arithmetic," IEEE Trans Very Large Scale (VLSI) Syst., vol. 6, no. 1, pp. 101 – 113, Mar 1998.

- [8] J. L. Massey and J. K Omura, "computation method and apparatus for finite field arithmetic," U.S.patent, 4, 587, 627, May 1986.

- [9] R. C. Mullin, "Multiple Bit multiplier," U.S. Patent 5, 787, 028, July 1998.

- [10] R.C.Mullin,I. M.Onyszchuk,S. A.Vanstone "Computational methods and apparatus for Finite field arithmetic," U.S.patent, 4,745,568, May 1988.

- [11] Peng Ning and Yiqun Lisa Yin, "Efficient Software implementation for finite field multiplication in normal basis," 2001.

- [12] E. D. Mastrovito "VLSI Architectures for Computations in Galois Fields," PhD thesis, Linkoping University, Dept. Electr. Eng., Linkoping, Sweden, 1991.

- [13] C. Y. Lee, E. H. Lu, and J. Y. Lee, "Bit parallel systolic Multipliers for GF (2<sup>m</sup>) fields defined by all-one and equally – spaced polynomials," IEEE Trans. Comput., vol. 50, no. 5, pp. 385–393, May 2001.

- [14] C. Y. Lee, "Low complexity bit parallel systolic multiplier over GF (2<sup>m</sup>) using irreducible trinomial," IEEE Comput. Digit. Tech., vol. 150, no. 1, 2003.

- [15] C.Y. Lee, "Low complexity parallel systolic Montgomery multipliers over GF(2<sup>m</sup>) using Toeplitz Matrix – vector representation," IEICE Trans. Fundam., 2008.

#### \*\*\*

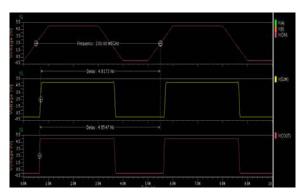

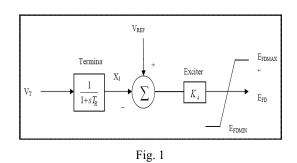

## Implementation of CMOS Full-Adders for Energy-Efficient Arithmetic Applications

#### S. Madhava Rao & K Amarnath

VRS&YRN Engineering college, Chirala, Prakasam(DT), A.P, INDIA,

*Abstract* - We present two high-speed and low-power full-adder cells designed with an alternative internal logic structure and passtransistor logic styles that lead to have a reduced power-delay product (PDP). We carried out a comparison against other full-adders reported as having a low PDP, in terms of speed, power consumption and area. All the full-adders were designed with a 0.18- m CMOS technology, and were tested using a comprehensive test bench that allowed to measure the current taken from the full-adder inputs, besides the current provided from the power-supply. Post-layout simulations show that the proposed full-adders outperform its counterparts exhibiting an average PDP advantage of 80%, with only 40% of relative area.

Index Terms—Arithmetic, full-adder, high-speed, low-power.

#### I. INTRODUCTION

Energy efficiency is one of the most required features for modern electronic systems designed for high-performance and/or portable applications. In one hand, the ever increasing market segment of portable electronic devices demands the availability of lowpower building blocks that enable the implementation of long-lasting battery-operated systems. On the other hand, the general trend of increasing operating frequencies and circuit complexity, in order to cope with the throughput needed in modern high-performance processing applications, requires the design of very high-speed circuits. The power-delay product (PDP) metric relates the amount of energy spent during the realization of a determined task, and stands as the more fair performance metric when comparing optimizations of a module designed and tested using different technologies, operating frequencies, and scenarios.

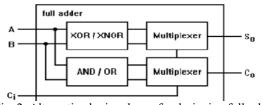

Addition is a fundamental arithmetic operation that is broadly used in many VLSI systems, such as application-specific digital signal processing (DSP) architectures and microprocessors. This module is the core of many arithmetic operations such as addition/subtraction, multiplication, division and address generation. As stated above, the PDP exhibited by the full-adder would affect the system's overall performance [1]. Thus, taking this fact into consideration, the design of a full-adder having lowpower consumption and low propagation delay results of great interest for the implementation of modern digital systems. In this paper, we report the design and performance comparison of two full-adder cells implemented with an alternative internal logic structure, based on the multiplexing of the Boolean functions XOR/ XNOR and AND/OR, to obtain balanced delays in SUM and CARRY outputs, respectively, and pass-transistor powerless/groundless logic styles, in order to reduce power consumption. The resultant full-adders show to be more efficient on regards of power consumption and delay when compared with other ones reported previously as good candidates to build low-power arithmetic modules.

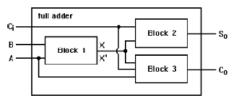

Fig. 1. Full-adder cell formed by three main logical

#### blocks.

This paper is organized as follows. Section II presents the internal logic structure adopted as standard in previous papers for designing a full-adder cell. Section III introduces the alternative internal logic structure and the pass-transistor powerless/groundless logic styles used to build the two proposed full-adders. Section IV explains the features of the simulation environment used for the comparison carried out to obtain the power and speed performance of the full-adders. Section V reviews the results obtained from the simulations, and Section VI concludes this work.

#### **II. PREVIOUS FULL-ADDER OPTIMIZATIONS**

Many papers have been published regarding the optimization of low-power full-adders, trying different options for the logic style (standard CMOS [2], differential cascade voltage switch (DCVS) [3], complementary pass-transistor logic (CPL) [4], double pass-transistor logic (DPL) [5], swing restored CPL (SR-CPL) [6], and hybrid styles [and the logic structure used to build the adder module. The internal logic structure shown in Fig. 1 has been adopted as the standard configuration in most of the enhancements developed for the 1-bit full-adder module. In this configuration, the adder module is formed by three main logical blocks: a XOR-XNOR gate to obtain  $A \oplus B$ (Block 1),  $\overline{A \oplus B}$  and XOR blocks or multiplexers to obtain the SUM (So) and CARRY (Co) outputs (Blocks 2 and 3). A deep comparative study to determine the best implementation for Block 1was presented in [13], and an important conclusion was pointed out in that work: the major problem regarding the propagation delay for a full-adder built with the logic structure shown in Fig. 1, is that it is necessary to obtain an intermediate  $A \oplus B$  signal and its complement, which are then used to drive other blocks to generate the final outputs. Thus, the overall propagation delay and, in most of the cases, the power consumption of the fulladder depend on the delay and voltage swing of the  $A \oplus B$  signal and its complement generated within the cell. So, to increase the operational speed of the fulladder, it is necessary to develop a new logic structure that does not require the generation of intermediate signals to control the selection or transmission of other signals located on the critical path.

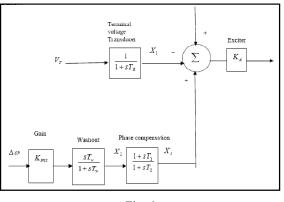

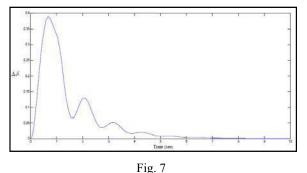

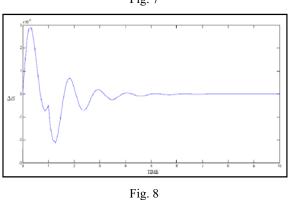

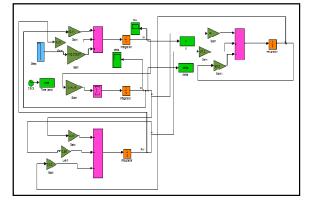

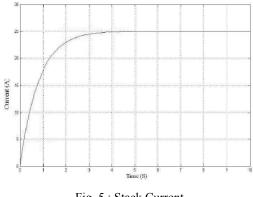

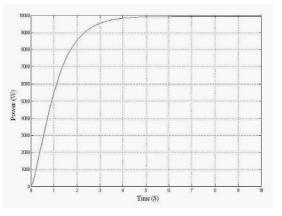

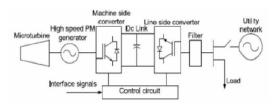

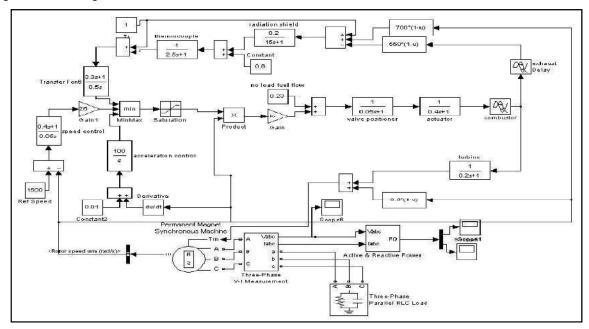

# III. ALTERNATIVE LOGIC STRUCTURE FOR A FULL-ADDER