#### Interscience Research Network

### Interscience Research Network

Conference Proceedings - Full Volumes

**IRNet Conference Proceedings**

5-20-2012

# International Conference on Electronics & Communication Engineering

Prof.Srikanta Patnaik Mentor IRNet India, patnaik\_srikanta@yahoo.co.in

Follow this and additional works at: https://www.interscience.in/conf\_proc\_volumes

Part of the Biomedical Commons, Controls and Control Theory Commons, Electrical and Electronics Commons, Electromagnetics and Photonics Commons, Nanotechnology Fabrication Commons, Power and Energy Commons, Signal Processing Commons, Systems and Communications Commons, and the VLSI and Circuits, Embedded and Hardware Systems Commons

#### **Recommended Citation**

Patnaik, Prof.Srikanta Mentor, "International Conference on Electronics & Communication Engineering" (2012). *Conference Proceedings - Full Volumes*. 77. https://www.interscience.in/conf\_proc\_volumes/77

This Book is brought to you for free and open access by the IRNet Conference Proceedings at Interscience Research Network. It has been accepted for inclusion in Conference Proceedings - Full Volumes by an authorized administrator of Interscience Research Network. For more information, please contact sritampatnaik@gmail.com.

# Proceedings of International Conference on ELECTRONICS & COMMUNICATION ENGINEERING

(ICECE-2012) 20<sup>th</sup> May, 2012 BANGALORE, India

Interscience Research Network (IRNet)

Bhubaneswar, India

## **Editorial**

Fast communication is the need of the hour for which society relies on Electronics &Telecommunication Engineering for breakthroughs in applications such as satellites, next generation mobile phones, air-traffic control, the Internet etc. In fact, all electronic devices need software interface to run and come with one or other device controlling programs architected and developed by electronics and communication Engineering. Thus, tremendous opportunities for research and development lies in the area of Electronics and Communication Engineering, as everyday consumer need new devices to support them in daily life.

International Conference on Electronics and Communication Engineering (ICECE-2012) provides such unique platform for R&D works. The conference will conglomerate academicians, researchers from all types of institutions and organizations who would share their domain knowledge and healthy interaction would take place covering the areas like electronics and communications engineering, electric energy, automation, control and instrumentation, computer and information technology, and the electrical engineering aspects of building services and aerospace engineering, The wide scope encompasses analogue and digital circuit design, microwave circuits and systems, optoelectronic circuits, photo voltaic, semiconductor devices, sensor technology, transport in electronic materials, VLSI technology and device processing.

We are happy to inform you that we had received an overwhelming response in the area. I must acknowledge your response to this conference. I ought to convey that this conference is only a little step towards knowledge and innovation but certainly in the right perspective. I wish all success to the paper presenters I extend heart full thanks to members of faculty from different institutions, research scholars, delegates, IRNet Family members, members of the technical and organizing committee. Above all I note the salutation towards the almighty.

Editor-in-Chief Dr. K. Karibasappa

Prof & Head, Dept. of Electronics & Communication Engineering Shavige Malleswara Hills Dayananda Sagar College of Engineering Kumaraswamy Layout BANGALORE -560078

# A GALS Chip Multiprocessor Architecture for Multi-Link Low-Area Interconnection

#### Haripriya. R, C.B.Vinutha & M.Z.Kurian

SSIT, Tumkur, Karnataka, India; Email: priyakushi18@gmail.com, cbvinutha@gmail.com, mzkurianvc@yahoo.com

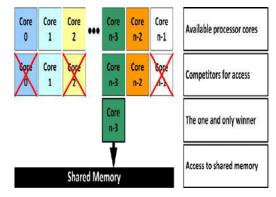

Abstract --- Integrating multiple processors into a single chip (known as chip multiprocessors or CMPs) has recently become easily achievable and common due to continuing advances in VLSI fabrication technologies A new inter-processor communication architecture for chip multiprocessors is proposed which has a low area cost, flexible routing capability, and supports globally asynchronous locally synchronous (GALS) clocking styles. A presented implementation example of the proposed architecture shows that it can reduce the communication circuitry area by approximately two times with similar routing capability. To achieve a low area cost, the proposed statically-configurable asymmetric architecture assigns large buffer resources to only the nearest neighbor interconnect and much smaller buffer resources for long distance interconnect. To maintain flexible routing capability, each neighboring processor pair has multiple connecting links. The architecture supports long distance communication in GALS systems by transferring the source clock with the data signals along the entire path for write synchronization. Compared to a traditional dynamically-configurable interconnect architecture with symmetric buffer allocation and single-links between neighboring processor pairs, this implementation has approximately two times smaller communication circuitry area with a similar routing capability.

**Key words:** Chip multiprocessor, globally asynchronous locally synchronous (GALS), inter-processor interconnect, many-core, multi-core, network-on-chip (NoC).

#### I. INTRODUCTION

A number of processors integrated on a singles chip performing various operations simultaneously is called System on chip(SOC). Wires in deep-sub micrometer CMOS fabrication technologies are introducing greater relative delay, relative power consumption, and timing and power variations which is causing traditional onchip communication methods such as a global bus structures to meet considerable challenges. Researchers have proposed network-on-chip (NoC) solutions which use routers for inter-processor communication. Most research is based on dynamic packet-switched routing architectures. Another approach is the statically configurable nearest-neighbor interconnect architecture where each processor communicates with only its four nearest neighbors in 2-D meshes and long distance communication is accomplished by software in intermediate processors. Other designs use both dynamic and static interconnects.

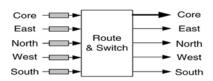

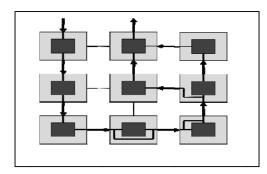

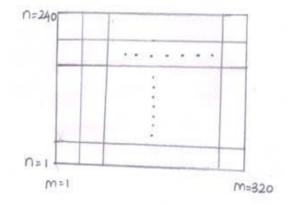

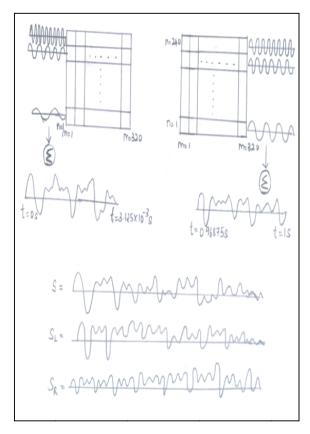

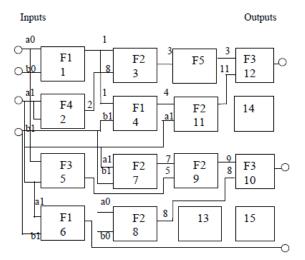

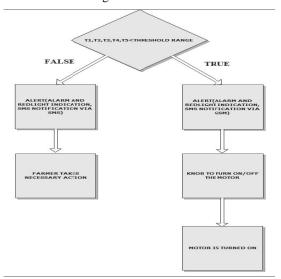

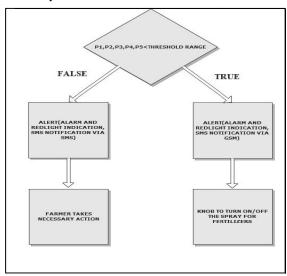

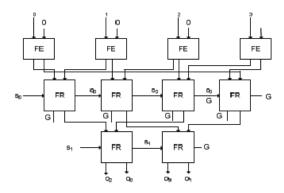

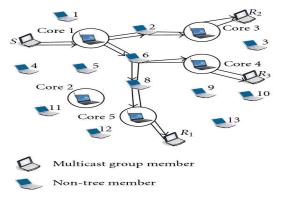

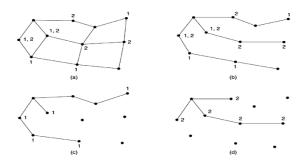

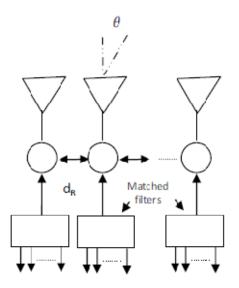

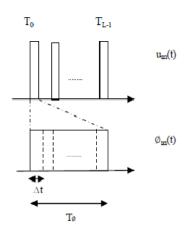

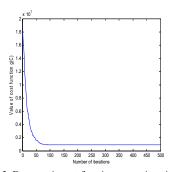

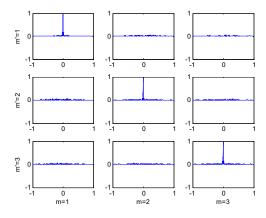

Fig.1.a. Illustration of interprocessor communication in a 2-D mesh

Although both dynamic routing architectures and static nearest neighbor interconnect architectures achieve significant success in specific areas, they have some limitations. Dynamic routing architectures are flexible, but normally require relatively large circuit area and power for communication circuitry. The static nearest neighbor interconnect architecture reduces area and power requirements significantly, but it results in relatively high latency for long distance communication.

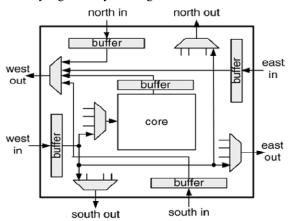

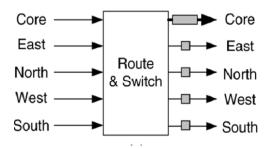

Fig.1.b. A generalized communication routing architecture in which only signals related to the west edge are drawn.

Communications within chip multiprocessors for many applications, especially many digital signal processing (DSP) algorithms, are often largely localized most communication is among nearest (or local) neighbors while a small portion is long distance. Motivated by this fact, we propose an *asymmetric* structure to obtain good tradeoffs between flexibility and cost by treating the nearest neighbor communication and long distance communication differently, using more buffer resources for nearest neighbor connections, and using fewer buffer resources for long distance connections. Together with the relatively simple static routing approach, this asymmetric architecture can achieve low area cost for communication circuitry.

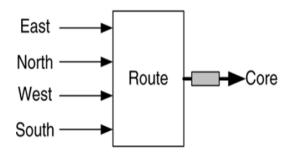

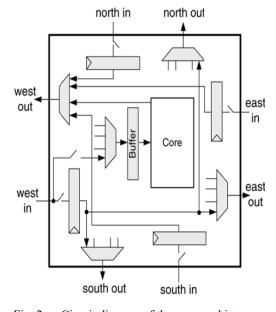

Fig.1.c. Illustration of interprocessor communication in a static neighbor interconnect architecture

Fig. 1.d. Circuitry diagrams of the static nearest neighbor interconnect architecture

Data from four inputs are transferred only to the processing core to reduce the circuitry cost, and only a single buffer is needed. Under the static asymmetric architecture, there are a couple of design options available such as the number of input ports (buffers) for the processing core and the number of links between each neighboring processor pair. The area, speed, and performance of different design options are analyzed,

and some conclusions based on the results are drawn. We found that increasing the number of links between processors is helpful to increase routing capability, but it dramatically increases processor area after a certain point which depends on implementation details.

Two or three links are generally appropriate when each processor in the chip utilizes a simple single-issue processor architecture. Moreover, the proposed architecture supports the globally asynchronous locally synchronous (GALS) clocking style which allows each processor to operate in its own clock domain and avoids the design of a global clock tree, which can significantly simplify the clock system design and potentially reduce system power consumption. After examining the characteristics of different approaches, we propose a source synchronous method which transfers the clock with the data and control signals along the entire path to the destination processor. Compared to traditional dynamically configurable interconnect architectures with symmetric buffer allocation and single links between each neighboring processor pair, a presented implementation example of the proposed architecture shows that it can reduce the communication circuitry area by approximately two times with similar routing capability.

#### A. Static Routing Versus Dynamic Routing

The inter-processor interconnect can be configured statically before runtime (static routing), or dynamically at runtime (dynamic routing). Dynamically-routed networks have been commonly used in multiprocessor systems such as those utilizing message passing methods. Moreover, dynamic networks have been rigorously studied in NoC research, but staticallyconfigured architectures have been much less intensively studied. The key advantage of the static configuration approach is that for applications with predictable traffic, such as most DSP applications, it can provide an efficient solution with small area cost and communication latency. The dynamic configuration solution can effectively address more applications because of its flexibility, but it has non-negligible overhead in terms of the circuitry area and the communication latency; the main overhead comes from the routing path definition, the arbiter of multiple independent clock sources, and the signal recognition at the destination processor.

#### B. Dynamic Routing and Its Overhead:

In dynamic routing, the data transfer path should be defined by the source processor and propagated to the corresponding downstream processor(s) or dynamically decided by intermediate processors. The circuitry to define and control the routing path has an area overhead, and to propagate the routing path might cost extra

instructions and increase the clock cycles for the data transfer. Since each link in the dynamic routing architecture is shared by multiple sources, an arbiter is required to allow only one source to access the link at one time. Furthermore, in GALS chip multiprocessors, this arbiter becomes more complex since it must handle multiple sources with unrelated clock domains. An obvious overhead is that some synchronization circuitry is required for the arbiter to receive the link-occupying request from different sources, and some logic is required to avoid glitches when the occupying path changes.

Another important issue is how the destination processor can identify the source processors of the received data. Since data can travel through multiple processors with unknown clock domains, it is not possible to assume a particular order for the incoming data. One common method is that an address is assigned to each processor and sent along with the data, and the destination processor uses the address to identify the source processor through software or hardware. Combining these overheads, the communication latency for dynamic routing between adjacent processors has been estimated to be typically larger than 20 clock cycles, and this value will increase further for GALS dynamic routing networks due to the additional synchronization latency.

#### C. Static Routing

Due to its smaller circuit area and excellent compatibility with GALS-clocked systems, we investigate only the static routing approach in this paper. Few multi-processor systems use static routing, and the Systolic approach is one of the pioneers. Systolic systems contain synchronously-operating processors which "pump" data regularly through a processor array, and the data to be processed must reach the processing unit at the exact predefined time. Due to this strict requirement for data streams, the systolic architecture is well suited only for applications with highly regular communication patterns such as matrix multiplication. Releasing the strict timing requirement of the data stream can significantly broaden the application domain. To release the systolic system's strict cycle-by-cycle timing requirements, each processor must "wait" for data when the data is late, and the data must "wait" to be processed when it comes early. Inserting a first-inputfirst-output (FIFO) with appropriate full and empty logic at each input of the processing core can meet these requirements. Data is buffered in the FIFO when it comes early, the downstream processor is stalled when the FIFO is empty and there is a read request, and the upstream processor is stalled when the FIFO is full and there is a write request. In this way, the requirement for the data stream is only its order, not its exact arrival

time. RAW is a chip multiprocessor with very low latency for interprocessor communication (three clock cycles) using both static routing and dynamic routing, but it achieves this goal with a large area cost of about 4 mm in a  $0.18\mu m$  CMOS technology. The communication circuitry we propose is suitable for broad applications, with low latency (about five clock cycles), and low area overhead (about 0.1 mm in  $0.18\mu m$  technology).

#### II. ARCHITECTURE DESIGN

Consider an example of a nine-processor JPEG encoder. Table shows the data traffic of each processor for a nine-processor JPEG encoder as shown in Fig. 2.a, which demonstrates the different asymmetric data traffic on the input-buffered and output-buffered routers. Considering the router's input ports, although each processor shows a clear asymmetric communication data traffic load, the major input direction for different processors are different which makes the overall traffic at the input ports within a factor of five in this example—the relative input traffic for the east, north, west, and south directions are 9%, 26%, 22%, and 43%, respectively. Therefore, to optimize buffers in this approach would require the customization of individual buffer sizes on each processor which would then unfortunately optimize the design for only one (or a small number) of applications.

On the other hand, considering the *output* ports, each processor shows a similar asymmetric data traffic: most of the data from the input ports are delivered to the core (for local processing) and very little is delivered to the edges (for long distance communication), and overall about 80% of the data are delivered to the core. Thus a single asymmetric output-buffered router can be widely suitable for different applications, which is important since multi-core chips utilizing NoC architectures are typically used widely across a number of application domains.

Fig. 2.a. Nine-processor implementation of a JPEG encoder core

#### A. Low-area interconnect architecture

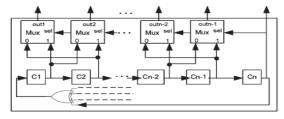

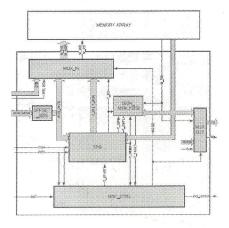

The proposed statically configurable low-area Asymmetrically-Buffered interconnect architecture.

Fig. 2.b. Block diagram of the proposed Router

|          | Network data words of Input ports of router                                |     |      |     |       |

|----------|----------------------------------------------------------------------------|-----|------|-----|-------|

|          | East                                                                       | Nor | th W | est | South |

| Relative | 9%                                                                         | 26% | 22   | %   | 43%   |

|          | Network data words of output ports of router<br>Core East North West South |     |      |     |       |

|          | l _                                                                        | _   |      | •   |       |

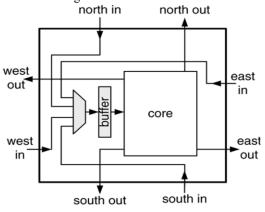

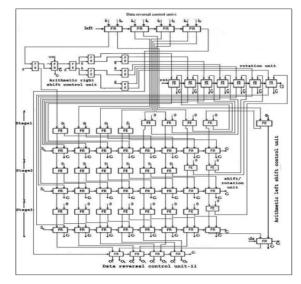

Fig. 2.c. Circuit diagram of the proposed interprocessor communication architecture

It has the asymmetric buffer resource for the long distance interconnect and the local core interconnect. Asymmetric Data Traffic Typically Exists at the Router's Output Ports. The case of varying buffer allocation for input buffered routers to match asymmetric inter-processor data traffic loads has been shown to achieve some benefits. In contrast, this paper presents asymmetric buffer allocation for output buffered routers because we find the asymmetric data traffic on the router's outputs and are more uniform across different applications and hence the architecture is helpful across a wider range of applications. The asymmetric traffic focuses on the differences in traffic going to the processor core versus output ports connected to other processors.

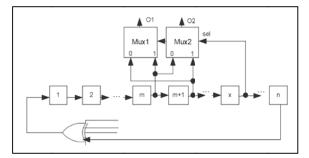

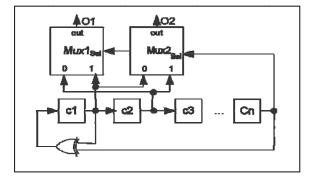

#### B. Working of proposed Multiprocessor architecture

Instead of equally distributing buffer resources to each output port, we allocate a relatively large buffer to the processing core port, and smaller buffers (one or several registers) to the other ports. Fig. 2.c shows the circuit diagram where only signals related to the west edge (west in and west out) are drawn. This architecture's circuit area is similar to the nearest neighbor interconnect architecture, shown in Fig. 2.c. Since it adds only a few registers and multiplexers. From the point of view of routing capability, this architecture is similar to the traditional dynamic routing architecture, shown in Fig. 1.b, since reducing the buffers in ports for long distance communication does not significantly affect system performance when the communication is localized. With its one large buffer for the processing core, the proposed architecture can save about five times the area compared to the traditional dynamic architecture shown in Fig. 1.b.

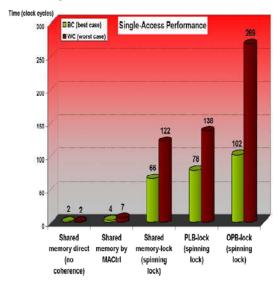

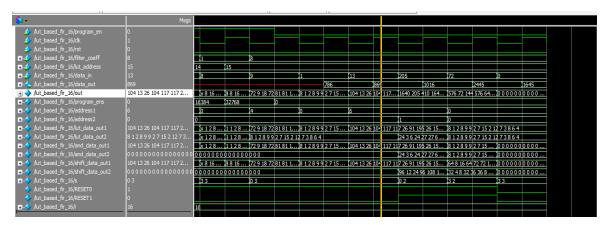

#### III. RESULTS COMPARISON

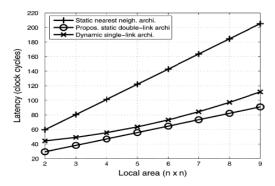

Different communication architectures, including the static nearest neighbor interconnect, the proposed double-link routing

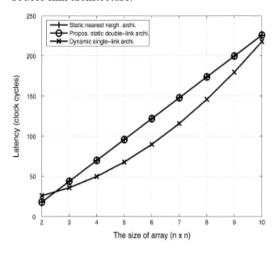

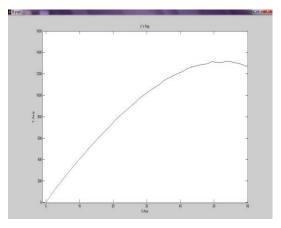

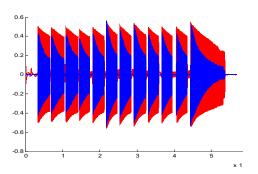

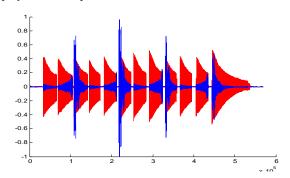

Fig. 3.a. . Performance Comparison

#### A. Performance Comparison

In this section, the analysis of performance of different implementations is done.

# 1) Performance of the Basic Communication Patterns:

Fig. 3.a shows the latency of the basic communication patterns mapped onto different architectures along with different array sizes.

The proposed double-link routing architecture normally has significant savings in communication latency compared to the nearest neighbor architecture. The latency of the dynamic single-link routing architecture is similar to the static double-link architecture. The modeled communication is organized uniformly by the four basic communication patterns and we assume 80% of the communication is within the local area which is the value often used in the literature. The proposed static double-link routing architecture is more than 2 times faster, and the dynamic single link routing architecture is a little slower than the static double link architecture.

Fig:3.b. Performance Comparison

#### IV. CONCLUSION

An asymmetric inter-processor communication architecture which assigns more buffer resources to the nearest neighbor interconnect and fewer buffer resources to the long distance interconnect is proposed. Static routing is emphasized due to its low cost and low communication latency. Compared to a traditional dynamically-configurable interconnect architecture with symmetric buffer allocation and single-links between neighboring processor pairs, this implementation has approximately two times smaller communication circuitry area with a similar routing capability. The

proposed architecture also provides the ability to support long distance GALS communication with an extended source synchronous transfer method. A single node is considered and its working is simulated and also network with multiple nodes is simulated for static and dynamic routing techniques. Next the proposed architecture code should be simulated and synthesized.

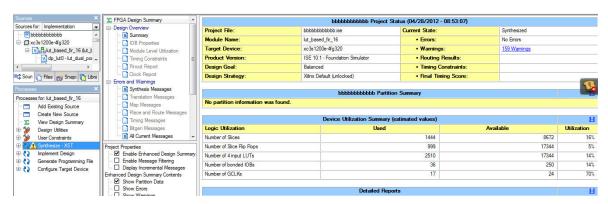

#### **HDL Synthesis Report**

Macro Statistics of existing system

# Registers : 19

1-bit register : 8

8-bit register : 11

# Latches : 1

8-bit latch : 1

Macro Statistics of Proposed system

8-bit Registers : 8

# Registers : 8

1-bit register :1

#### REFERENCE

- [1] M. B. Taylor, J. Kim, J. Miller, D. Wentzlaff, F. Ghodrat, B. Greenwald, H. Hoffman, P. Johnson, W. Lee, A. Saraf, N. Shnidman, V. Strumpen, S. Amarasinghe, and A. Agarwal, "A 16-issue multiple-programcounter microprocessor with point-to-point scalar operand network," in *Proc. ISSCC*, Feb. 2003, pp. 170–171.

- [2] S. W. Keckler, D. Burger, C. R. Moore, R. Nagarajan, K. Sankaralingam, V. Agarwal, M. S. Hrishikesh, N. Ranganathan, and P. Shivakumar, "A wire-delay scalable microprocessor architecture for high performance systems," in *Proc. ISSCC*, 2003, vol. 46, pp. 168–169.

- [3] W. Dally and B. Towles, "Route packets, not wires: On-chip interconnection networks," in *Proc. IEEE Int. Conf. Des. Autom.*, Jun. 2001, pp. 684–689.

- [4] S. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, D. Finan, P. Iyer, A. Singh, T. Jacob, S. Jain, S. Venkataraman, Y. Hoskote, and N. Borkar, "An 80-tile 1.28 TFLOPS networkon-chip in 65 nm CMOS," in *Proc. ISSCC*, Feb. 2007, pp. 98–99.

- [5] B. Baas, Z. Yu, M. Meeuwsen, O. Sattari, R. Apperson, E. Work, J.Webb, M. Lai, T. Mohsenin, D. Truong, and J. Cheung, "AsAP: A fine-grain multi-core platform for DSP

- applications," *IEEE Micro*, vol. 27, no. 2, pp. 34–45, Mar./Apr. 2007.

- [6] Z. Yu, M. Meeuwsen, R. Apperson, O. Sattari, M. Lai, J. Webb, E. Work, D. Truong, T. Mohsenin, and B. Baas, "AsAP: An asynchronous array of simple processors," *IEEE J. Solid-State Circuits*, vol. 43, no. 3, pp. 695–705, Mar. 2008.

- [7] D.Wentzlaff, P. Griffin, H. Hoffmann, L. Bao, B. Edwards, C. Ramey, M. Mattina, C. Miao, J. F. Brown III, and A. Agarwal, "On-chip interconnection architecture of the tile processor," *IEEE Micro*, vol. 27, no. 5, pp. 15–31, Sep./Oct. 2007.

- [8] H. Zhang, M. Wan, V. George, and J. Rabaey, "Interconnect architecture exploration for low-energy reconfigurable single-chip DSPs," in *Proc. IEEE Comput. Soc. Workshop VLSI*, Apr. 1999, pp. 2–8.

- [9] P. P. Pande, C. Grecu, M. Jones, A. Ivanov, and R. Saleh, "Effect of traffic localization on energy dissipation in NoC-based interconnect," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2005, pp. 1774–1777.

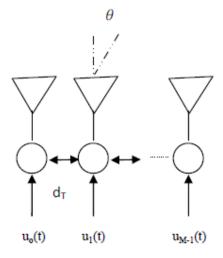

# Performance Analysis of WSXC and WIXC SSM OXC in WDM Optical Networks

#### Md. Ishtiaque Aziz Zahed & Md. Shah Afran

Department of Electrical and Electronic Engineering Bangladesh University of Engineering and Technology (BUET), Dhaka-1000, Bangladesh. E-mail: ishtiaque2307@gmail.com, afran2902@gmail.com

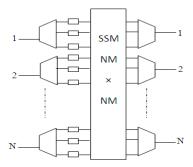

Abstract - The impact of inband crosstalk on an optical signal passing through optical cross-connect nodes (OXC's) in wavelength division multiplexing (WDM) optical network, is studied from the equation of electric field with crosstalk and the corresponding current. The analysis has been done for two SSM (space switching matrix) OXC architecture namely WSXC & WIXC where later one has full wavelength conversion capability. Although WIXC attenuates more crosstalk though it is found that depending on the values of optical propagation delay differences, coherent time of lasers and time duration of one bit of the signal, the required power penalty in WIXC may be greater than that of WSXC in some cases. The analysis has been performed on the measures of Bit Error Rate (BER) and Power Penalty.

**Keywords**- Inband crosstalk, optical cross-connect, wavelength division multiplexing (WDM), wavelength selective cross-connect (WSXC), wavelength interchanging cross-connect (WIXC).

#### I. INTRODUCTION

In a wavelength division multiplexing (WDM) optical network, the optical cross-connect (OXC) at each node carries out wavelength sensitive switching in optical form without restoring to electro optical conversion. A number of OXC architectures have been proposed in [1] and [2], each of which has its own unique features, strengths and limitations. While cross-connecting wavelengths from input to output fibers OXC introduces inband and intraband crosstalk. The inband crosstalk which is also known as homodyne crosstalk has the same wavelength as the signal and degrades the transmission performance seriously. When an optical signal passes through an OXC, many crosstalk contributions are combined with the signal[3]-[5].

In this paper, the performance of wavelength selective cross-connect (WSXC), wavelength interchanging cross-connect (WIXC) is investigated and compared in the presence of inband (Homodyne) crosstalk which is caused by non-ideal performance of an optical node.

#### II. INBAND CROSSTALK IN WSXC AND WIXC

Inband crosstalk is a major problem in optical network.

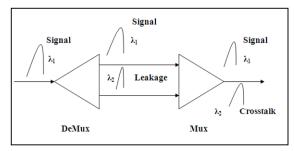

Figure. 1 A cascaded wavelength demultiplexer and multiplexer as a source of in-band crosstalk

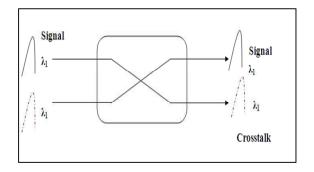

Figure. 2 An optical switch as a source of in-band crosstalk

One source of this arises from cascading a demultiplexer with wavelength wavelength multiplexer as shown in Figure 1. The demux ideally separates the incoming wavelengths to different output fibers. In reality however a portion of the signal at one wavelength, say  $\lambda_i$ , leaks into the adjacent channel  $\lambda_{i+1}$ because of non ideal suppression within the demux. When the wavelengths are combined again into a single fiber by the mux, a small portion of the  $\lambda_i$ , that leaked into the  $\lambda_{i+1}$  channel, will also leak back into the common fiber at the output. Although both signals contain the same data, they are not in phase with each other, due to different delays encountered by them. This causes inband crosstalk. [6]

Another source of this type of crosstalk arises from optical switches as shown in Figure 2, due to the non ideal isolation of one switch port from the other. In this case, the signal contains different data. The crosstalk penalty is highest when the crosstalk signal is exactly out of phase with the desired signal.

Inband crosstalk can be divided into coherent crosstalk and incoherent crosstalk. When the phase of the crosstalk signal is correlated with that of the main signal, it is called coherent crosstalk. When the phase of the crosstalk signal is not correlated with that of the main signal, it is called incoherent crosstalk. Crosstalk signals generated from the same source are coherent crosstalk and crosstalk signals generated from different sources are incoherent crosstalk. Coherent crosstalk is believed not to cause noise but causes fluctuations of signal power.

The lightpath, representing the optical layer connection between the source-destination node pairs, can be set up through the intermediate OXCs in either a wavelength- continuous (WC or VWP, virtual wavelength path) or non-wavelength-continuous (NWC or WP, wavelength path) fashion. In the WC case, the same wavelength is used over the entire lightpath whereas, in the NWC case, different wavelengths may be used in different optical links along the given path. Setting up the lightpath would not only involve selecting the route to be followed but also the wavelengths to be used along the selected route[6].

Wavelength conversions at the intermediate nodes is necessary if NWC (WP) lightpaths are to be supported. This, however, would require the OXCs to do wavelength conversion in addition to their switching functions. The OXCs may, in turn, be classified based on their wavelength conversion capability [6].

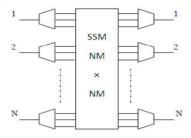

Among a number of proposed SSM OXC structures WSXC and WIXC are focused. An OXC without any conversion capability is called a wavelength selective cross-connect (WSXC) whereas an OXC with full

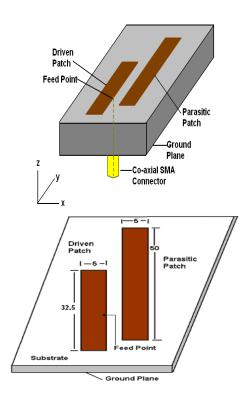

conversion capability is referred to as a wavelength interchanging cross-connect (WIXC). Examples of these have been shown in the figure 3 and 4.

Here, SSM refers to the space switching matrix, used to switch the optical signals without doing any wavelength conversion. The wavelength converters required have been shown separately.

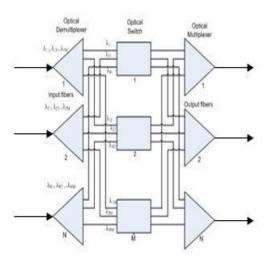

A typical structure of OXC is shown in figure 5, which consists a total of N optical demultiplexers, M optical switches and N multiplexers. Each of the input fibers to an optical demultiplexer contains M different wavelengths. Each of these passes through an optical switch before they are combined with the outputs from the other M-I optical switches.

Assuming the OXC is fully loaded the OXC will be interfered by M+N-2 homodyne crosstalk contributions, N-I of which are leaked by the optical switch leaked by the (OXC) demultiplexer / multiplexer pair. [7]

If we consider the signal with wavelength 1 in input fiber 1, noted as  $\lambda_{11}$  or the main signal.  $\lambda_{11}$  will be interfered by N-I crosstalk contributions leaked from the N-I signals with wavelength 1 in the other N-I input fibers. Similarly, when each signal with wavelength 1 is demultiplexed to one path, there will be a fraction of it in each of the other M-1 outputs of the corresponding demultiplexer because of the non-ideal

Figure. 3 WSXC OXC architecture

Figure. 4 WIXC OXC architecture

Figure. 5 Typical structure of an Optical Cross Connect

crosstalk specification of optical demultiplexers. These M-1 crosstalk contributions can be leaked from any signal with wavelength 1 in all the N input fibers. The number of contributions leaked from each signal is random, from 0 to M-I, depending on the cross connecting state of the OXC. Defining  $X_1$  as the number of contributions leaked from  $\lambda_{11}$  in a given state of the OXC,

$$X_1 \in [0,M\text{-}1]$$

Defining,  $X_j$ ( j=[2,N] ) as the number of contributions leaked from  $\lambda_{j1}$  fin the same state of the OXC, taking into account the N-1 contributions leaked by the optical switch 1, we have

$$X_j \in [1, M]$$

and

$$X_1 + \sum_{j=2}^{N} X_j = M + N - 2$$

The field of the main signal and all the M+N-2 crosstalk contributions can be expressed as

$$\vec{E}(t) = Eb_s(t)\cos[\omega_s t + \Phi_s(t)] \vec{P}_s$$

$$+ \sum_{i=1}^{X_1} \sqrt{\varepsilon} E b_s(t - \tau_i) \cos[\omega_s (t - \tau_i) + \Phi_s(t - \tau_i)] \vec{P}_t$$

$$+ \sum_{j=2}^{N} \sum_{k=1}^{X_j} \sqrt{\varepsilon} E b_j (t - \tau_{jk}) \cos[\omega_j (t - \tau_{jk}) + \Phi_j (t - \tau_{jk})] \vec{P}_{jk}$$

(1)

Where E is the signal field amplitude which is assumed to be unchanged as the leaked power is rather low; bs(t) and bj(t) (j=[2,N]) are the binary data

sequences with values of 0 or 1 in a bit period T of  $\lambda_{11}$  and  $\lambda_{j1}$ , respectively,  $\omega_{\rm s}(t), \Phi_{\rm s}(t),$  $\omega_i(t), \Phi_i(t)$  are the center frequencies and phase noises of the lasers, respectively,  $\overrightarrow{P_s}$  is the unit magnitude polarization vector of the signal;  $\tau_i$ ,  $\tau_{ik}$  and  $\overrightarrow{P_l}$ ,  $\overrightarrow{P_{lk}}$  are the propagation delay differences and unit magnitude polarization vectors of the contributions, respectively;  $\varepsilon$  is the optical power ratio of each crosstalk contribution to the signal and for simplicity we assume all the crosstalk contribution have the same power.,  $\overrightarrow{P_s}$ ,  $\overrightarrow{P_t}$  and  $\overrightarrow{P_{tk}}$  are treated as time invariant here as they change rather slowly compared to the bit period. Now depending on relation between  $\tau_i$ ,  $\tau_{jk}$ ,  $\tau_{coherent}$  and T three cases may be considered for which the laser relative intensity noise (RIN) will get different values [7].

### **Case 1:** If $\tau(\tau_i and \tau_{jk}) > \tau_{coherent}$ :

As  $\Phi_s(t)$  is uncorrelated with  $\Phi_s(t-\tau_i)$  and  $\Phi_j(t-\tau_{jk})$  are also uncorrelated with each other for different k. In that case the noise power can be expressed as

$$\sigma_{RIN,1}^{2} = \varepsilon \sum_{l=1}^{M+N-2} \cos^{2} \theta_{l}$$

$$\cos \theta_{l} = \overrightarrow{P}_{s} \cdot \overrightarrow{P}_{l}$$

(2)

where,  $\theta_l$  is the polarization angle difference between the *l*th crosstalk contribution and the signal.

If  $\tau(\tau_i and \tau_{jk}) < \tau_{coherent}$ : Depending on the relation between  $\tau$  and T two cases may arise.

Case 2(a): If

$$\tau(\tau_i and \tau_{ik}) \ll T$$

:

As  $b_s(t - \tau_i)$  equal to  $b_s(t)$  approximately in this case, so coherent crosstalk do not cause noise but causes fluctuation. So, noise power will be  $\sigma_{RIN,2a}^2 \varepsilon \sum_{j=2}^{N} (\sum_{k=1}^{X_j} \cos\phi_{jk} \cos\phi_{jk})^2$  (3)

Case 2(b): If

$$\tau(\tau_i and \tau_{ik}) > T$$

:

As  $b_s(t - \tau_i)$  becomes completely incorrelated with  $b_s(t)$  due to unsynchronus nature of  $b_s(t)$  the noise power will be

$$\sigma_{RIN,2b}^2 = \frac{1}{3} \varepsilon \sum_{i=1}^{X_1} (\cos\phi_i \cos\theta_{jk})^2 + \varepsilon \sum_{j=2}^{N} (\sum_{k=1}^{X_j} \cos\phi_{jk} \cos\theta_{jk})^2$$

(4)

For worst case scenario with fully loaded OXC for the above cases crosstalk may be expressed as

$$\sigma_{RIN,1}^{2} = \varepsilon(M+N-2)$$

$$\sigma_{RIN,2a}^{2} = \varepsilon M(N-1)$$

$$\sigma_{RIN,2b}^{2} = \frac{1}{3} \varepsilon M + \varepsilon M(N-1)$$

(6)

$$(7)$$

#### III. EXPERIMENTS AND DISCUSSIONS

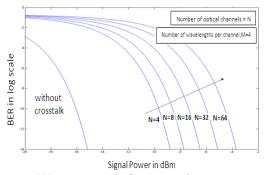

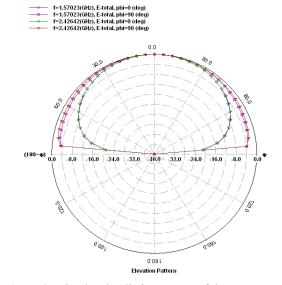

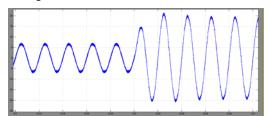

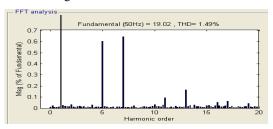

The detail analysis of Homodyne crosstalk is described in section 2. Figure 3 and Figure 4 shows WSXC and WIXC architectures. Inband crosstalk induced RIN due to these OXCs is given by equations 1-4 for both coherent and incoherent case. Case 1 represents the incoherent inband crosstalk while there are 2 cases for coherent inband crosstalk.

Case 2a occurs when optical propagation delay differences are much less than the time duration of one bit ( $\tau$ <<T) which means  $b_s(t-\tau_i)$ == $b_s(t)$ . Again case 2b represent the case when  $\tau$ >T and  $b_s(t-\tau_i)$  become uncorrelated completely with  $b_s(t)$  as  $b_s(t)$  is a random sequence and they are not synchronized. The To observe the BER performance we assumed the worst case scenario and simulated equation 5-7 incorporating the Homodyne crosstalk induced RIN into these equations. To evaluate the expression of  $\sigma_{th}$  as given by equation

$$\sigma_{th}^2 = (4kTB_e/L)$$

(8)

we assumed, T=300K, k=1.38x10^-2^3,  $B_e\!=\!10^9$  Hz and  $R_L\!=\!50$  Hz.

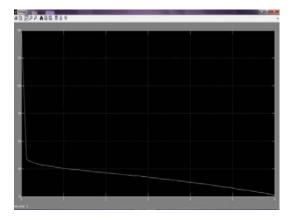

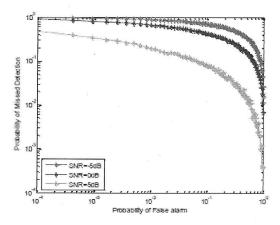

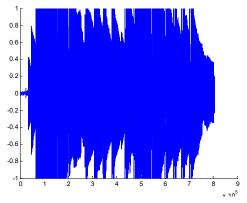

Figure 6 gives the comparative plots of BER against the signal power for WSXC OXC having number of wavelengths per channel, M=4 and separately for case1, case 2a and case2b . In plots of figure 4.1[(a)-(c)], the number of channels, N is varied as  $N=[4\ 8\ 16\ 32\ 64]$  and it is found that the BER increases significantly with increase.

Figure. 6(a) BER performance in presence of incoherent homodyne crosstalk (case 1) for WSXC OXC with varying number of channels and with no. of wavelengths per channel=4

Figure. 6(b) BER performance in presence of coherent homodyne crosstalk for  $\tau$ <<T (case 2a) for WSXC OXC with varying number of channels and with no. of wavelengths per channel=4

Figure. 6(c) BER performance in presence of coherent homodyne crosstalk for  $\tau << T$  (case 2a) for WSXC OXC with varying number of channels and with no. of wavelengths per channel=4

of N. It is also evident from the curves that incoherent crosstalk results in lower BER than that of coherent crosstalk.

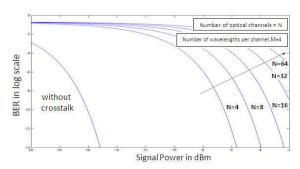

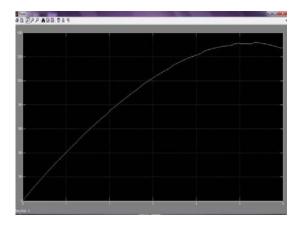

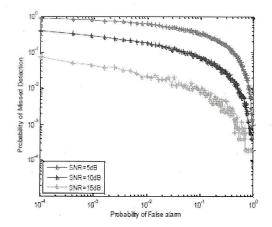

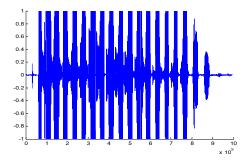

Similar results have been found for WIXC OXC in Figure 7 keeping all the parameters same. Here we can notice the BER curves are shifted which means power requirements are different for a specific BER in between these architectures.

Figure. 7(a) BER performance in presence of incoherent homodyne crosstalk (case 1) for WIXC OXC with varying number of channels and with no. of wavelengths per channel=4

Figure. 7(b) BER performance in presence of coherent homodyne crosstalk for  $\tau << T$  (case 2a) for WIXC OXC with varying number of channels and with no. of wavelengths per channel=4

Figure. 7(c) BER performance in presence of coherent homodyne crosstalk for  $\tau$ << T (case 2a) for WIXC OXC with varying number of channels and with no. of wavelengths per channel=4

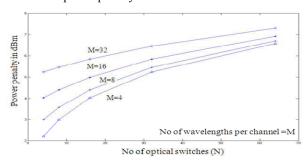

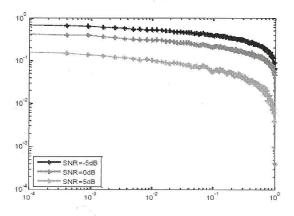

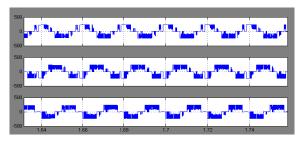

Figure 8 shows the plot of power penalty against number of channels due to the incoherent homodyne crosstalk induced RIN in a WSXC architecture shown in figure. The data for the calculation of power penalty is taken for a standard BER of 10<sup>-9</sup>. The plot shows that with increase of number of channels power penalty increases. The effect of number of wavelength per channel on power penalty and the

Figure. 8 Power penalty as a function of number of channels for different number of wavelengths per channel for incoherent homodyne crosstalk in WSXC OXC. Power penalty is plotted to get an overall BER of 10<sup>-9</sup>. The data is obtained from figure 6

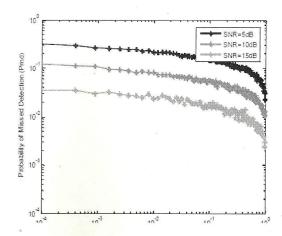

Figure. 9 Power penalty as a function of number of channels for different number of wavelengths per channel for incoherent homodyne crosstalk in WIXC OXC. Power penalty is plotted to get an overall BER of 10<sup>-9</sup>. The data is obtained from figure 7.

Results are also shown in figure 8.We have got an upward shift of power penalty against number of channels for an increase in number wavelength per channel. Figure 9 gives similar plot for WIXC architecture.

#### **CONCLUSIONS**

We have calculated all the power penalties considering the worst case scenario, but this requirement may be relaxed if the probability distribution function (PDF) is known for the phase noise of the laser and the polarization angle differences.

#### ACKNOWLEDGMENT

Special thanks to Dr. Satya Prasad Majumder for the cordial cooperation. He helped a lot making us understand the topics in the easiest way.

#### REFERENCES

- [1] S.Okamoto, A. Watanabe, and K. Sato, "Optical path cross-connect node architectures for photonic transport network," J. Lightwave Technol., vol. 14, no. 6, pp. 1410-1422, Jun, 1996

- [2] E. Iannone and R. Sabella, "Optical path technologies: A comparison among different cross-connect architectures," J. Lightwave Technol., vol. 14, no. 10, pp. 2184-2194, Oct,1996.

- [3] E.L.Goldstein, L.Eskildsein and A.F. Elrefaie. "Performance implications of component crosstalk in transparent lightwave networks," IEEE Photon Technol. Lett., vol. 6, pp. 657-660, May 1994.

- [4] C. S. Li and F. Tong," Crosstalk and interference penalty in all optical networks using static wavelength routers," J. Lightwave Technol., vol. 14, pp. 1120-1126, Jun,1996.

- [5] H. Takahashi, K. Oda, and H. Toba, "Impact of crosstalk in an arrayed waveguide multiplexer on N×N optical interconnection," J. Lightwave Technol., vol. 14, pp. 1097-1105, Jun,1996.

- [6] Teck Yoong Chai, Tee Hiang Cheng, Gangxiang Shen, Sanjay K. Bose, and Chao Lu," Design and performance of optical cross-connect architectures with converter sharing," Optical Networks Magazine, pp.73-83,July/August 2002

- [7] Yunfeng Shen, Kejie Lu, and Wanyi Gu, Member, "Coherent and Incoherent Crosstalk in WDM Optical Networks," J. Lightwave Technol., vol. 17, no.5, pp. 759-764, May,1999

### **Distributed Shared Files Management**

#### Saurabh Malgaonkar<sup>1</sup>, Onkar Jambhale<sup>2</sup> & Manish Bhelande<sup>3</sup>

<sup>1</sup> Thadomal Shahani College of Engineering, Mumbai

<sup>2</sup> Ramrao Adik Institute of Technology, NaviMumbai

<sup>3</sup> Vidyalankar Institute of Technology, Mumbai

E-mail: <sup>1</sup>saurabhmalgaonkar@gmail, <sup>2</sup>onkar.ony@gmail.com, <sup>3</sup>manishbhelande@gmail.com

Abstract - Most often file sharing is the common and basic requirement when users work on a particular domain or area of interest. Users can use software that connects in to a peer-to-peer network to access shared files on the computers of other users (i.e. peers) connected to the network. Files of interest can then be downloaded directly from other users on the network. So this concept is similar to a distributed file system where files are distributed across the network but the users have an illusion of a centralized file system and also avoids its high complexity and cost of implementation.

Keywords- P2P File Access; Network Sharing; Distributed Shared File System; Large File Sharing.

#### I. INTRODUCTION

In a computer system a file is a named object that comes into existence by explicit creation, is immune to temporary failures in the system and persists until explicitly destroyed. The two main purposes of using files are as follows:

- 1. Permanent storage of information.

- 2. Sharing of information.

A user creates many files on his machine and updates them accordingly if required. Access made to those files depends on the requirements of the user. Most often file sharing is the common and basic requirement when users work on a particular domain or area of interest. Example, in a hospital, the records of the patients are essential in every department so they are shared accordingly on the system. So users need to share the files that are necessary and access those shared files quickly. So file sharing becomes the practice of distributing or providing access to digitally stored information such as computer programs, multimedia (audio, images, and video), documents, or electronic books. It may implemented through a variety of ways. Common methods of storage, transmission, and distribution[1] used in file sharing include manual sharing using removable media, centralized server on computer networks, World Wide Web-based hyperlinked documents and the use of distributed peer-to-peer networking[1][2].

Users can use software that connects in to a peer-to-peer network to access shared files on the

computers of other users (i.e. peers) connected to the network. Files of interest can then be downloaded directly from other users on the network. So this concept is similar to a distributed file system where files are distributed across the network but the users have an illusion of a centralized file system and also avoids its high complexity and cost of implementation.

The most common and feasible approach is to use peer to peer file sharing[2] for implementing a distributed shared files management system. In addition to these advantages it will also enable to support the following:

- Remote Information Sharing: It will enable to access to information that is being shared by a remote machine.

- User Mobility: As the system will reflect all the files shared by the nodes present in the system, user can access them from anywhere.

- 3. Availability: For better fault tolerance, the systems shared file entries are available to the users even in the temporary failure of the main directory controller.

The file sharing domain is necessary and distributed thus need further justification on using peer to peer technologies[2] on that domain. Peer to peer file sharing is economically efficient When the user wants to find specific information, searching for the same would require a lot of human efforts and time. If the upcoming technologies are clubbed with the existing ones it can help better

understand the whole system. Thus extending the idea of peer to peer in the file sharing environment helps better built the whole system. For accomplishing this task a directory server is used to better organize the user shared files information in the related domain.

The main advantages of this approach are:

- 1. Scalability: It can easily accommodate more users and hence making it more scalable.

- 2. Bandwidth: It will enable to save the network bandwidth as only the required files when required are transmitted among the users.

- 3. Distributed control: In this, there is a need for a central point which we name as a controller, which will manage various shared file lists from all the clients and will be handling the shared file lists distribution scenario as per the clients entry or exit in the network.

- 4. Fault Tolerance: The plan is to make this file sharing scenario fault tolerant so a replica controller will be maintained that will be frequently updated from the primary controller so even if the primary controller fails the system continues to operate.

The goal of this project is not only to achieve a distributed shared files management system that will allow clients that are distributed location wise to share files among themselves but also to give better performance in terms of file access.

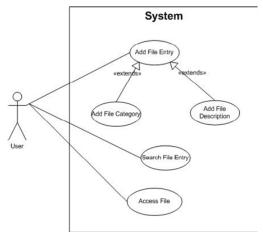

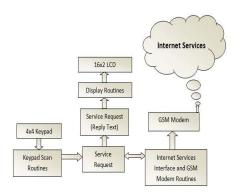

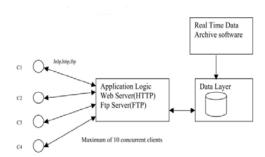

A diagrammatic interaction of the user with the system is as follows:

Figure 1. User Interaction with the System

When a user interacts with the system when joined to a particular network, the user adds the file entry that needs to be shared among the clients in the

network. The user mentions the category of the file and also adds its description so the other users are aware about the contents of the file. A user can also search for a particular file entry from the required parameters (name, category or description) as the users in a network can share hundreds of file entries and it is impossible to look for a particular entry manually. Once the user finds the required file entry, the user with its help can access the file by receiving it from the client who is sharing that particular file. A common interface in each client also lists the overall shared file entries of all the clients in the network for access along with the search mechanism.

# II. TYPICAL P2P DISTRIBUTED FILE SHARING SYSTEM

We present a literature review which includes the basic file sharing details, distributed file system, various technologies, existing communication protocols etc. The development of file sharing system has triggered two to three decades ago.

As the various file applications grew from hundreds to thousands to millions, the interest along with the resources for file sharing. File sharing began in 1999 with the introduction of Napster[3][4], a file sharing program and directory server that linked people who had files with those who requested files. The central index server was meant to index all of the current users and to search their computers. When someone searched for a file, the server would find all of the available copies of that file and present them to the user. The files would be transferred between the two private computers. While Napster connected users through a directory server, these new services connected users remotely to each other. These services also allowed users to download files other than music, such as movies and games. One limitation was that only music files could be shared. After Napster shut down the most popular of these new services was Gnutella[5].

#### A. P2P System Advantages

In [7] the key features in P2P file transfer are highlighted. Using P2P technique, execute nodes can share data with each other instead of fetching files only from the central manager or a file server, saving plenty of time. In a typical file sharing environment which follows a centralized approach where the files need to be shared are transferred to the central server and the nodes accessing them from it has its great disadvantage. In case of the failure of the central server the entire system comes to a standstill and when the system is operating on heavy load the central server becomes a bottleneck. Also it does not reflect the updated file entries, so when a

user updates a file, it needs to be uploaded again to the central server. So this paper suggest a peer to peer sharing where all the major disadvantage of a centralized sharing system have been taken care off.

#### B. A Basic P2P File Sharing System

In [8] a reliable and simple P2P file sharing system is described which avoids unnecessary data redundancy and connectivity issues among peers by maintaining an adapter which optimizes the working of the entire file sharing system. This approach also makes it highly scalable in nature. Since a file resides at local node and is shared only when required there is no need for separate update policy, the shared file itself reflects the updates version of the file all the time as the user updates it. The adapter maintains a list of all the files that are shared by the users and updates it accordingly then sends it to all the users. When this list is imported by the users they can perform file sharing operations among themselves.

#### C. Reilablity and fault tolerance

The disadvantages of a client server file system which do not scale with respect to the number of users and exhibit a single point failure are further highlighted in [6]. So the focus is more on the distributed peer to peer aspect rather than a centralized one. The important aspect of this paper is fault tolerance achieved by replicating data, hence the data being available even in case of temporary failures. The other aspect to be considered is user mobility.

#### III. DSFM DESIGN

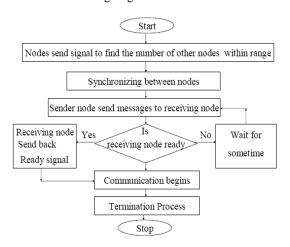

It is necessary to keep the system in a constant flow and achieve the targeted goals of the proposed system at the same time. So the after studying carefully all the literatures [6][7][8] and highlighting the key features and drawbacks from them, the overall workflow of the proposed system will be as follows:

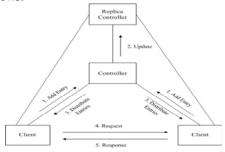

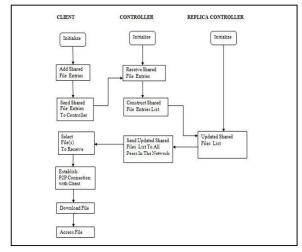

Figure 2. Overall System Workflow

The three most important components of the system are:

- 1. Client: The client system will allow the clients to share the files that are required as well as provide an interface that will allow the client to access the files shared by all the nodes in the system(centralized view of shared files). When a client joins the network its shared files will be added to the system and when the client leaves the network all his shared files entries are discarded from the system. After a client receives the updated shared files list, it can access the file from the respective clients.

- 2. Controller: The main controller will store the address and shared files information of the client peers and will be responsible for distributing them to all the clients in the network. It's basic task is just to index the file entries from all the clients and distribute them accordingly. Also when a client joins or leaves the network it will update its shared files entries accordingly and inform the remaining clients. So through the controller we will be able to achieve the scenario of overall file sharing.

- 3. Replica Controller: The project plans to replicate the main controller so even when the main module fails temporary the system does not comes to a standstill, the requests can be handled from the replica controller and the system continues to operate. So our system will be fault tolerant.

#### A. General Basic Functionality

The following diagram denotes the basic interaction among the modules and functionality of each module. This is the normal scenario highlighted when the system is working with the primary controller when fully functional.

Figure 3. General Flow Chart

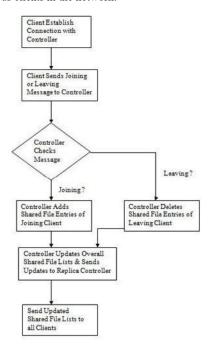

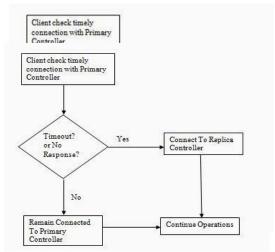

#### B. File Sharing Process

The following diagram illustrates the scenario that enables to achieve the basic file sharing process among the various clients in the network.

Figure 4. Basic File Sharing Process

#### C. Fault Tolerance Scenario

The following diagram illustrates the scenario about how the clients detect the temporary no response or failure of the primary controller and redirect to the replica controller.

Figure 5. Handling Primary Controller Failure

#### REFERENCES

- [1] Kenneth P. Birman (2005), "Reliable distributed systems".

- [2] Rüdiger Schollmeier, "A Definition of Peer-to-Peer Networking for the Classification of Peerto-Peer Architectures and Applications", Proceedings of the First International Conference on Peer-to-Peer Computing IEEE, pp.149-160, 2002.

- [3] Menta, Richard, "Napster Clones Crush Napster. Take 6 out of the Top 10 Downloads CNet", MP3Newswire,http://www.mp3newswire.net/stories/2001/topclones.html, July 20, 2011.

- [4] Ante, Spencer, "Inside Napster". Business Week. Retrieved 2011-04-10, http://www.businessweek.com/2000/00\_33/b3694 001.htm, June 7,2011.

- [5] "Gnutella File Sharing", http://slashdot.org/story/00/03/14/0949234/Open-Source-Napster-Gnutella, 15 August 2011.

- [6] Sunil Chakravarthy and Chittranjan Hota, "Secure Resilient High Performance File System for Distributed Systems", IEEE International Conference on Computer & Communication Technology, pp. 87-92, 2010.

- [7] Gao Ying, Liu Guan Yao and Huang JianCong, "A New Method of File Transfer In Computational Grid Using P2P Technique", IEEE International Conference on Network Computing and Information Security, pp. 332-336, 2011.

- [8] Rui Zhao, Ruhua Liu and Guangxuan Fu, "P2P File Sharing Software in IPv4/IPv6 IEEE International Conference on Software and networks, pp. 367-370, 2011.

## Location Cache Design Using Way Prediction Method for Chip Multiprocessors

#### Jyoti Guttedar, G.Jyothi & M.Z.Kurian

Department of EC, Sri Siddhartha Institute of Technology, Sri Siddhartha University, Tumkur, Karnataka, India Email: jyotiec23@gmail.com, grandhejyothi@gmail.com, mzkurianvc@yahoo.com

Abstract - Recent research at Intel suggests that chips with hundreds of processor cores are possible in the not-so-distant future. As the number of cores grows, so does the size of the cache systems required to allow them to operate efficiently. Caches have grown to consume a significant percentage of the power utilized by a processor. In this research, we extend the concept of location cache to support chip multiprocessors (CMPs) systems in combination with low-power L2 caches.

Keywords—Cache architecture, dynamic and leakage power dissipation, location cache, low-power design, power analysis.

#### I. INTRODUCTION

In recent years, microprocessor companies have had difficulty in increasing the performance of CPUs by simply increasing their clock frequencies. Research has moved to parallelism in an effort to maintain performance increases [1], [2]. It is now increasingly common for multiple processor cores to be included on a single silicon die, creating what is called a chip multiprocessor (CMP). A CMP typically contains multiple cores operating at the same clock frequency, and those cores tend to share at least part of their cache system on the chip. For example, an Intel Xeon MP processor contains a pair of processor cores, and includes a cache system consisting of private L1 and L2 caches in addition to a large L3 cache that is shared between the cores [3].

As cache systems have grown in size to satisfy the additional needs of these CMP systems, so does the amount of power they consume. Several techniques, such as subbanking [4], [5], bitline segmentation [4], and phased cache [5]–[7] are commonly used to reduce the amount of dynamic power used by a cache. In addition, the increased power consumption may also lead to thermal issues on the chip, and design must proceed carefully in order to eliminate potentially-damaging hot spots. Several different techniques, such as gated-Vdd, drowsy caches, and DRG-caches, have been presented to reduce sub-threshold leakage power.

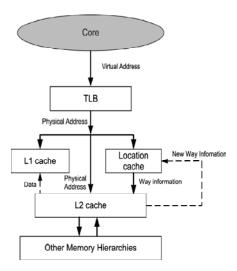

A location cache is a small direct-mapped cache that stores information relating an address to its location in the target cache [8]. This capability can save dynamic power upon cache reads and writes. More importantly, this behavior is capable of being exploited when used in combination with low-leakage techniques to save a significant amount of leakage power.

#### II. BACKGROUND

This section discusses the working principal and design of the location cache concept [8], for a single-core processor. Here, we assume that L2 is the highest level cache.

#### A. Structure of Location Cache

The location cache shown in Fig. 1 is a small direct-mapped cache, using address affinity information to provide the accurate location information for L2 cache [8]. The proposed location cache technique reduces the L2 cache power consumption, when compared with a conventional set-associative L2 cache. Depending on the L2 cache architecture, a location cache can be physically addressed or virtually addressed. Fig. 1 illustrates a revised L2 cache system architecture with a location cache, which is physically addressed.

In this physically addressed cache system, the location cache is physically addressed as well. It caches the access way location information of the L2 cache (the

way number in one set where a memory reference falls). This cache works in parallel with the L1 cache. As a location cache tries to cache the L2 location information, the block address (composed of the index address and the tag address) of the location cache should be of the same length as that of the L2 cache.

Fig.1. Physically addressed location cache architecture

#### B. Working Principle of Location Cache

The proposed cache system works in the following way. The location cache is accessed in parallel with the L1 cache. If the L1 cache sees a hit, then the result obtained from the location cache is discarded. If there is a miss in the L1 cache and a hit in the location cache, the L2 cache is accessed as a direct-mapped cache and the access power of the L2 cache will be greatly reduced .When both the L1 cache and the location cache see a miss, the L2 cache is accessed as a conventional setassociative cache and the content (i.e., the new way information) of the location cache is updated. When the location cache stores the location (way) information of the L2 cache, it uses the same block address as the L2 cache, instead of the L1 cache. As opposed to the wayprediction methods, the cached location is not a prediction. Even if there is a location cache miss, we do not see any extra delay penalty as seen in wayprediction caches.

Normally, the block size of the L2 cache is larger than that of the L1 cache; for instance, in Intel Itanium 2, the L1 block size is 64 bytes while the L2 block size is 128 bytes. Due to this difference in L1 and L2 block sizes, the location cache can still catch many references which are L1 misses but location cache hits.

#### III. LOCATION CACHES ON CMP SYSTEMS

Previous works utilizing location caches have been limited to single processor systems [8]. With multicore chips becoming increasingly prevalent, the concept of location cache needs to be adapted to these new types of systems. The following discussions describe two approaches to creating location caches capable of functioning within CMP systems.

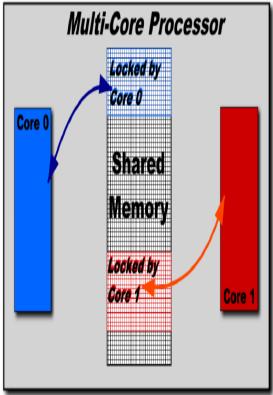

#### A. Shared Location Caches in CMP Systems

The most straightforward approach to adding a location cache to a CMP system involves sharing. Multicore processors commonly share an L2 or L3 cache among all of the cores. Similarly, it is possible to create a single location cache capable of being accessed by each of the cores in the system if those cores share a cache at some level. For example, if all four cores share a single L2 cache, these cores can be served by a single location cache.

If those four cores instead share a pair of L2 caches, a shared location cache approach can be implemented in two different ways: 1) cores sharing the same L2 cache also share the same location cache as shown in Fig. 2 and 2) all cores share only a single location cache.

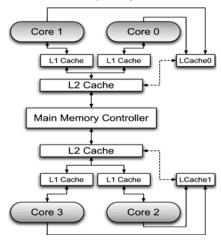

Fig. 2. CMP cache system using shared location caches.

In the case where the highest-level cache is L2, the location cache operates on every access initiated by every processor core it serves. The source of the access is completely disregarded, and only the transaction's address is taken into consideration. We only focus on the cache system shown in Fig. 2 with four cores sharing two location caches, since this architecture has been applied by commercial multi-core processors. Though this architecture is in fact a semi-shared location cache system, for each L2 cache, it is a purely shared location cache system. With all cores sharing a single location cache is not practical, because this architecture suffers

location cache line replacement problems as will be discussed later. That is, too many cores are fighting for a limited number of location cache lines and this makes the single location cache almost useless. Further, the (single) location cache has to store extra information such as the L2 where a specific data exists.

Assume Core 0 initiates a memory access. Its L1 cache and shared location cache LCache0 parse the tag and index information and check for matches. If the L1 cache hits, the result of the location cache access is ignored and L1 returns the requested data to the core. If the L1 cache misses, the result of the location cache access determines how to proceed. If the location cache also hits, the way information stored in the location cache is used to access the L2 cache as if it were directmapped. If the location cache hits, a hit in L2 is guaranteed. If the location cache misses, L2 is accessed in its normal set-associative manner and the new way information is provided to the location cache for future use. Note, however, that a miss in the location cache would not necessarily indicate a miss in the L2 cache. Now assume Core 1 attempts to access the same memory address, and it is not found in its L1 cache. The way information for this address was previously stored in the location cache by Core 0, and can now be used to access L2 as a direct-mapped cache.

Let us consider another example. Assume that the L1 caches of both Core 0 and Core 1 have cached the same line of data. Core 0 now performs a write to this address, changing the data. At this point the MESI protocol triggers the L1 of Core 1 to change the corresponding line's state from Shared to Invalid, and the newly-updated line in Core 0's L1 will retain its Shared status. Note that the corresponding line in the location cache does not need to be removed or modified, as it still points to the correct location in L2. If Core 1 now tries to access this address again, it will find that its own copy in L1 is marked Invalid. It can now use the shared location cache, which still knows the location of the line in L2, to access L2 as if it were a direct-mapped cache. In this case a location cache can be very useful for programs that require multiple cores accessing the same memory location.

Other than the simplicity of implementation, the other advantage to this configuration is that it lacks any coherency issues. Since all of the memory transactions sharing the same L2 cache pass through the same location cache, no additional implementation changes are required to keep the location cache and its target cache coherent. As a matter of fact, the location cache associated with each L2 cache just stores whether a specific data is in L2. If yes, what is the way number. The coherency mechanisms implemented in L1 and L2 are still serving their purposes. Thus, the function of

location cache and coherency protocols implemented in L1 and L2 are orthogonal.

In addition, with multiple cores expecting complete accesses to a location cache, the location cache will need a read and write port for every core supported. Simultaneous accesses to the same line in the location cache will increase latency, and reduce the efficiency of the location cache itself. Resolving these issues will increase both the complexity and power consumption of the location cache.

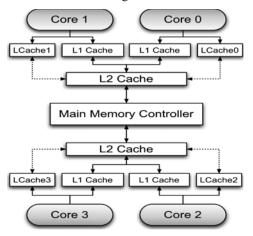

#### **B.** Private Location Caches in CMP Systems

A cache system utilizing a private location cache for each core is shown in Fig. 3.

Fig. 3. CMP cache system using private location caches.

When used in a CMP system, the simplistic location cache design is prone to incoherency when multiple location caches assist a single target cache (e.g., L2). For example, if Core 0 writes a value into its L2 cache, the way information is then stored in Core 0's location cache (LCache0). Later, if Core 1 writes a value into the L2 cache it shares with Core 0 and evicts this previous entry from L2, Core 0's location cache now points to data that is no longer present. Due to this possibility, it is necessary to extend the concept of location cache presented above for a CMP system.

Here location cache design is extended with a simplified version of the MESI protocol. This modification can be performed by adding only a single additional bit to each line in the location cache. This bit will determine whether the location cache line is in a Shared or Invalid state as shown in Fig. 4. A line in a location cache is marked Invalid if the line it references is no longer present in the target cache or if the line has not yet been written to. In all other cases, the line is marked Shared.

Fig. 4. Location cache coherency-state transition.

When a location cache lookup is performed, in order for a location cache hit to occur, the following two conditions must be satisfied:

- 1) requested line must be present in the location cache;

- 2) requested line must be marked Shared.

This alteration does not come without a cost. In order to perform this operation, additional care needs to be taken when lines are evicted from the target cache. When such an eviction occurs in the target cache, the tag and index portion of this reference is passed to each of the connected location caches. The location caches then check if they contain lines matching the newly-evicted entry. If the evicted transaction address is not present in other location caches, no further operation is performed. However, if the evicted transaction address is present in the other location caches, the lines in the location caches are marked Invalid by transition "LOC\_INV" (i.e., location cache invalid) as shown in Fig. 4. This will prevent future use of these location cache lines, which will be overwritten at the next opportunity.

The operation of location caches here is a little different from that of the shared case. When the way information is stored for a transaction initiated by Core 0, for example, it is stored in Core 0's private location cache. This location cache, LCache0, cannot be read from or written to by Core 1. This alleviates the problem where each core is constantly overwriting each other's cache information, and results in increased location cache hit rates.

However, let us say Core 0 has way information for a transaction stored in its private location cache. Now Core 1 performs an access that ultimately results in the line pointed to by Core 0's location cache being evicted from L2. Core 0's location cache now points to an address that no longer exists in L2. Here our coherency protocol would require L2 to transmit the address of the evicted L2 line to each of its connected location caches. If that address is present in any line of a location cache, the location cache line is marked Invalid. This ensures our private location caches remaining coherent. It should be noted that the location cache line is updated and changed to the shared state only when a message

from the L2 cache is received back at the L1 cache again. The way information of the particular block in the L2 cache is sent along with the message that is sent from the L2 cache to the L1 cache. The update occurs when any data message is received by the L1 cache from the L2 cache.

#### IV. CONCLUSION AND FUTURE WORK

Here the power savings realized by utilizing location caches in a CMP system is analyzed. The working principal of location cache for a single-core processor is reviewed, and extensions to this principal are proposed to allow location caches to support a CMP system. It is found that the amount of power saved by adding location caches varies quite significantly depending upon the setup of the tested parameters. The tested location caches were able to save power over all tested configurations and benchmarks, though they were far more effective at reducing the amount of leakage power than dynamic power. The number of entries in each location cache displayed a surprisingly small effect on the cache's overall power savings, with only about six of the benchmarks showing sensitivity to this parameter.

Looking towards possible future work, we suggest the following:

1) extension of this work to a cache system connected by network-on-chip (NoC); 2) learning the effect of OS techniques on the power savings provided by location caches in CMP systems; 3) extension of the current model to efficiently serve CMPs with dozens or even hundreds of cores; 4) extension of location caches to deal with exclusive caches; and 5) identifying the reasons why some benchmarks such as Radix(Ocean) seem to highly (or least) benefit from location caches.

#### V. ACKNOWLEDGEMENT

I hereby acknowledge to my project guide G.JYOTHI, LECTURER, department of E&C, S.S.I.T for her guidance, constant encouragement and wholehearted support. My special gratitude to Dr.M.Z.KURIAN, HOD, department of EC, S.S.I.T for his guidance, constant encouragement and wholehearted support to make this project a success.

#### REFERENCES

- [1] S. Vangal *et al.*, "An 80-Tile 1.28TFLOPS network-on-chip in 65nm CMOS," in *Proc. IEEE Int. Solid-State Circuits Conf.*, 2007, pp.98–589.

- [2] R. Varada, S. Tam, J. Benoit, and K. Chou, "SOC design challenges in a multi-threaded 65 nm dual

- core Xeon MP processor," in *Proc. Int.SOC Conf.*, 2006, pp. 217–220.

- [3] S. Rusu *et al.*, "A 65-nm dual-core multithreaded Xeon processor with 16-MB L3 cache," *IEEE J. Solid-State Circuits*, vol. 42, no. 1, pp. 17–25, Jan. 2007.

- [4] K. Ghose and M. B. Kamble, "Reducing power in superscalar processor caches using subbanking, multiple line buffers and bit-line segmentation," in *Proc. Int. Symp. Low Power Electron. Des.*, 1999, pp. 70–75.

- [5] C. Su and A. Despain, "Cache design tradeoffs for power and performance optimization: A case study," in *Proc. Int. Symp. Low Power Electron. Des.*, 1997, pp. 63–68.

- [6] T. Lyon, E. Delano, C. McNairy, and D. Mulla, "Data cache design considerations for the itanium2 processor," in *Proc. IEEE Int. Conf. Comput. Des.: VLSI Comput. Process. (ICCD)*, 2002, pp. 356–362.

- [7] A. Hasegawa, I. Kawasaki, K. Yamada, S. Yoshioka, S. Kawasaki, and P. Biswas, "Sh3: High code density, low power," *IEEE Micro*, vol. 15, no. 6, pp. 11–19, Dec. 1995.

- [8] M. Rui, W. B. Jone, and Y. Hu, "Location cache: A low-power L2 cache system," in *Proc. ACM/IEEE Int. Symp. Low Power Electron. Des.*, 2004,pp,120-125.

## Design and Implementation of Secure Low Cost Novel Remote Metering System Using GPRS

#### Nagaraj A. Hanchinamani & Chandrakala. V

Dr. Ambedkar Institute of Technology, Bangalore – 560056 \

E-mail: nagarajhanchinmani@gmail.com, v chandu9@yahoo.co.in

Abstract - Gradual improvement of Automatic Meter Reading System (AMRS) technology could be one-step ahead by using GPRS/EDGE modem. AMRS based on GPRS modem provides many advantages compared to other remote metering techniques. it uses TCP/IP and PPP protocol for communication and GPRS is an extension of GSM provides higher data transmission speed and more security. The benefits of implementing such system include robust data transmission, wide area network coverage, lowering power consumption, cost-effective and reliable. An interface system (IS) has been developed that can be plugged in existing digital energy meter and a new meter can also be developed with this IS. The proposed IS collects meter data and send that data to the server using GPRS modem. Each IS is capable of two-way communication. To send meter data existing GPRS networks have been used. This paper describes the detail hardware design of an interface system, step by step procedure of TCP/IP, PPP, and USB protocol implementation. The paper also shows the data transmission and reception with server end in real world.

Keywords: AMR, GSM, GPRS, IS,TCP/IP.

#### I. INTRODUCTION

Electricity is the source of power behind the development of any country. Due to increase number of power consumers in every sector such as residential, commercial and in industrial and scarcity in fossil fuel, it is essential to ensure proper use of energy and to generate correct bills and invoices and to reduce corruption. The conventional method of collecting meter data is done manually by assigning a person. It may involve dilemma such as human error and corruption. The Automatic Meter Reading System (AMRS) has completely changed the process of collecting meter readings. There are two types of AMR system: wirebased and wireless. Power Line Carrier (PLC) and Telephone Line Network are wire-based AMR system. The problems of wire-based AMR system are transmission distance, transmission cost, maintenance and security of data transmission. GSM, GPRS, WiFi, WiMax are the typical wireless based AMRS system. The wireless based AMRS system provides higher data collection speed and more efficiency. As there is no human intervention in the entire process, there is no chance of human error and corruption. In addition to this, the meter reading can be collected after any desired time interval such as hourly, daily, weekly, or monthly basis. Moreover, the electric supplier can take advantage of the wireless communication companies for remote monitoring and providing information to the customers anytime and anywhere. The Retail Providers will also be

able to offer new innovative products in addition to customizing packages for their customers. In Automatic meter reading system, it is very essential to develop a proper networking mechanism where the data transfer will be in high speed, will provide great security and will be cost-effective. Recently, there are many on going research experiments for implementation of electronic meters and the utilization of existing telecommunications systems to transmit meter reading automatically in fast, secured and accurate manner. The communication networks like the internet, GSM/GPRS networks provide useful means of communication due to its good area coverage capability and cost effectiveness. GPRS also supports for leading communication protocol such as IP and X.25 and the most important step GPRS is on the path to 3G. If SMS over GPRS is used, an SMS transmission speed of about 30 SMS messages per minute may be achieved. This is much faster than using the ordinary SMS over GSM, whose SMS transmission speed is about 6 to 10 SMS messages per minute. The gradual improvement of AMRS could be one-step ahead by using the USB GPRS/EDGE modem. However, USB modem utilize the TCP/IP and PPP protocol for communication and TCP/IP is a connection-oriented protocol, which provides reliable, secure and fast data transmission. The reliability and speed of communication could also be one-step ahead by interfacing USB modem rather than other modems for communication.

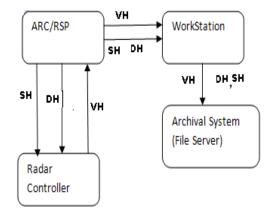

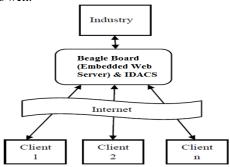

#### II. AMRS-SYSTEM OVERVIEW

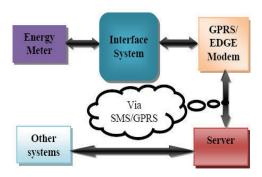

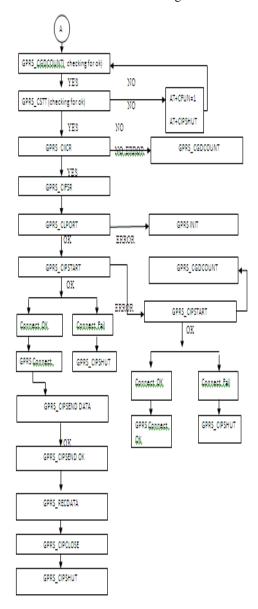

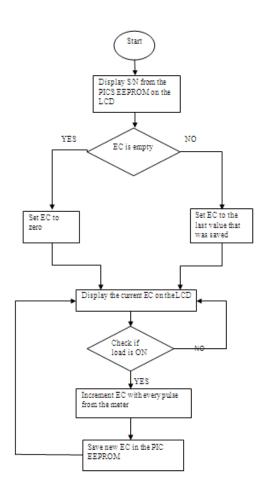

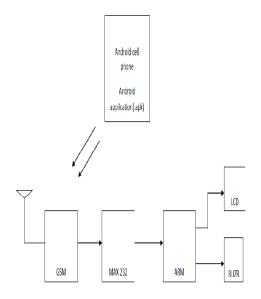

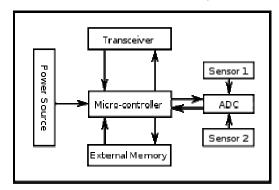

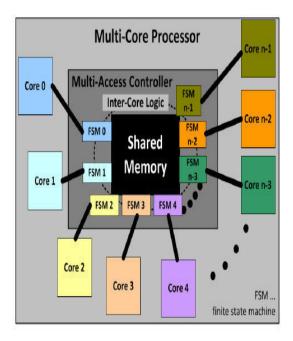

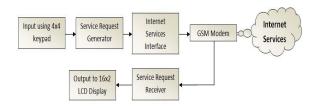

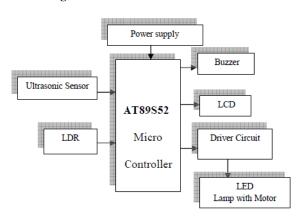

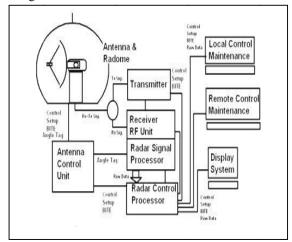

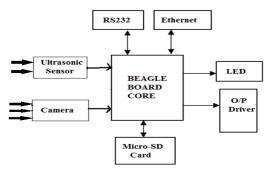

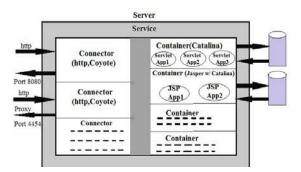

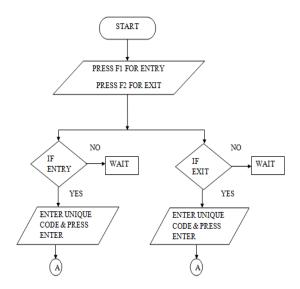

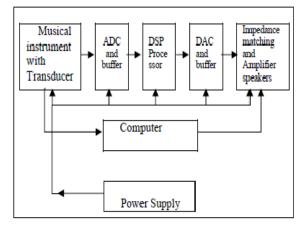

In this project, an interface system (IS) has been developed which will communicate with the digital meter and a USB GPRS/EDGE modem. The IS generates meter reading based on the meter pulses and sends that reading to the server database. Each IS is capable of two-way communication hence the meter can be controlled form the server for some specific purposes. The billing office should have a highly secure database system through which only the authorized staff members of the electricity supply company able to read and print electricity bills [9]. Other systems may be connected to the server for further process such as the online billing operation, providing security code, alarm system, temper detection [3], [10]. The system architecture of automatic meter reading system has given below in figure-1 through a block diagram.

Figure: 1: Block Diagram of Automatic Meter Reading System (AMRS)

#### A. Interface System

The interface system consists of a MCT2 Optocoupler, Microcontroller (MCU), modem and power regulation unit.

#### MCT2 Optocoupler

Interfacing can be done in many ways with the meter – by hacking the MCU of the meter and then capture the data, or by decoding the display output or by counting the pulses of the meter, or placing a parallel meter with the actual meter embedding an AMR system. Counting pulse and using that counting value to generate meter data is a great solution. So in the IS, light dependent resistors is used to sense the LED blinking. Generally two basic sensor circuits can be developed. The first is activated by darkness; the second is activated by light [11]. In this project, a light activated sensor circuit has been developed for a number of reasons to reduce the interference between the circuits, simultaneous separation and intensification of a signal and high voltage separation.

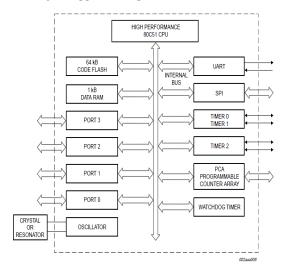

#### • The Core – Microcontroller Unit

The main function of the microcontroller unit (MCU) is to control the communication among the remote unit, the modem, and other different components. To select a suitable MCU for this project several matters have to keep in mind such as program memory size and type, speed, connectivity, USB On-The-Go (OTG) compatibility, analog to digital converter (ADC) features, USART etc. PIC24 and PIC32 series by Microchip MCU have been chosen because it satisfies the requirements of the project such as low power consumption, two-wire communication port, full duplex UART, ADC etc.

#### Interfacing with Modem.

Interfacing the USB device with microcontroller is typically based on the operating mode of microcontroller whether the microcontroller is in host mode or it is in device mode. If the microcontroller is in device mode then again two conditions arises that it is Bus power device or Self power device. If the microcontroller is in Host mode then the microcontroller has to be run with either external 3V to 3.6V power supply or external 5V power supply.

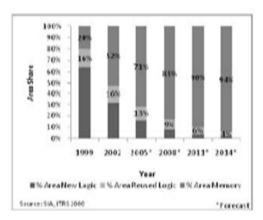

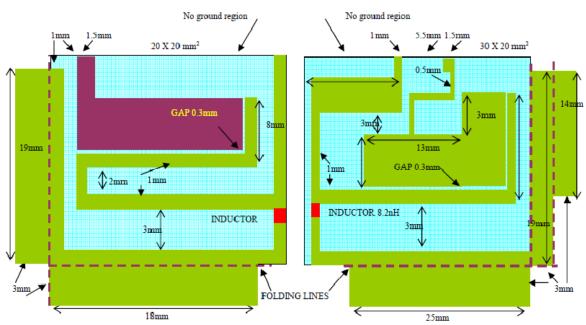

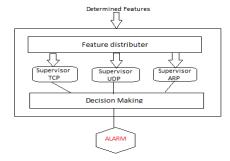

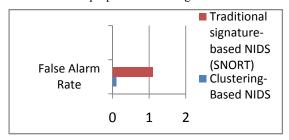

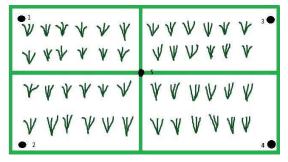

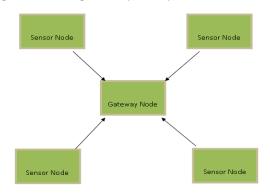

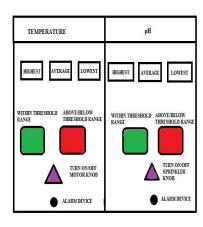

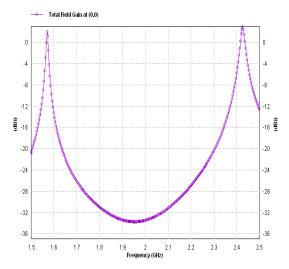

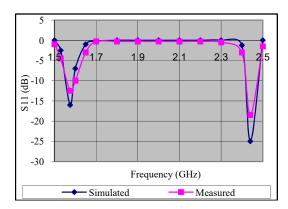

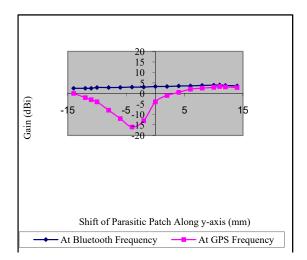

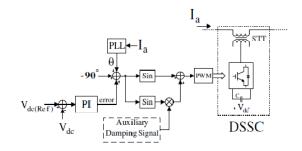

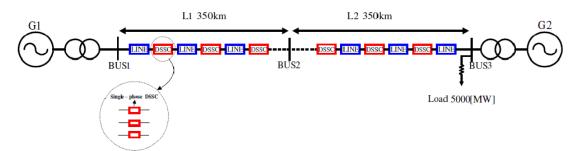

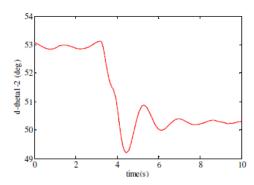

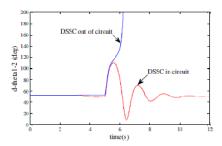

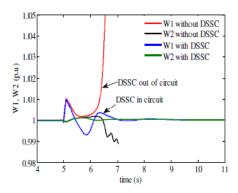

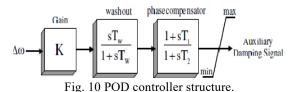

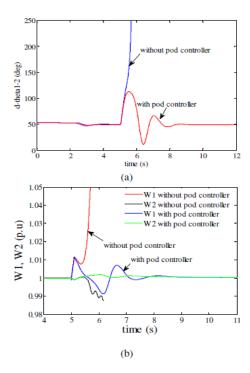

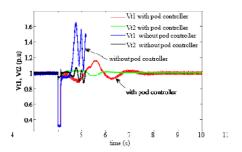

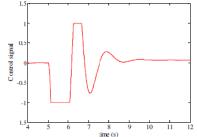

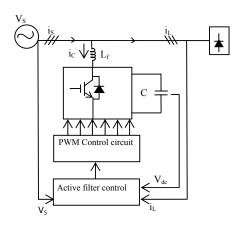

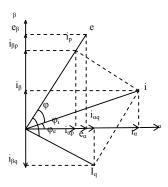

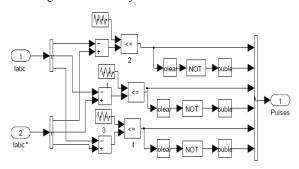

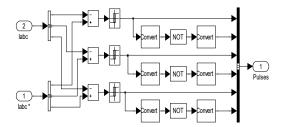

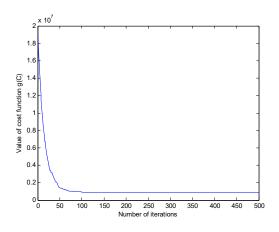

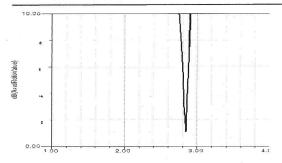

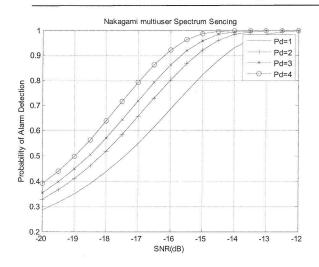

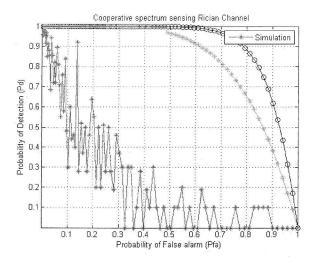

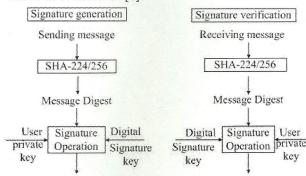

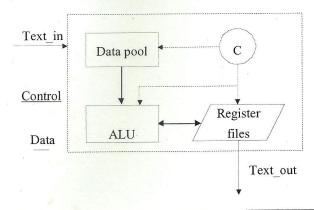

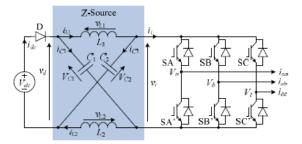

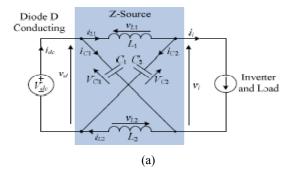

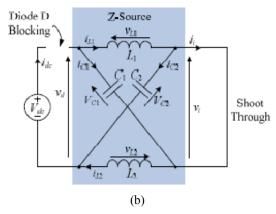

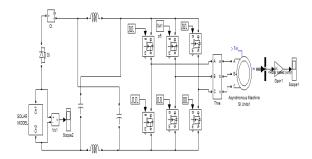

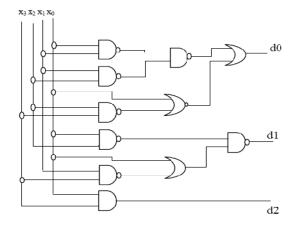

#### • Power regulation unit.